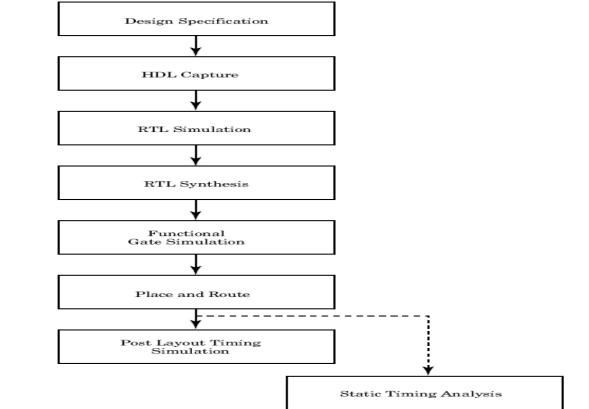

15 - High level design flowA.Carini – Progettazione di sistemi elettronici

# High level design flow

## From design specifications to RTL model

- The specifications must specify what the system does and must give the information necessary for building the design.

- The specifications are typically written in the language of the designer.

- Sometimes the specifications are given in terms of a behavioral HDL model.

- More often, it is the designer himself that writes a behavioral model in order to verify that the specifications are clearly stated.

- Then, the designer writes a synthesizable RLT description of the system.

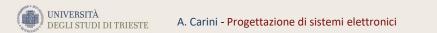

## **RTL simulation**

- After removing all syntax and semantic errors, the designer verifies the code by means of an RTL simulation.

- The designer uses appropriate test benches for driving the VHDL model and for checking that the results are correct.

- The VHDL description is analyzed, elaborated and executed by a VHDL simulator.

- The simulator output data, provided in a textual form or a waveform form, are used for verifying the design correctness and for finding possible errors.

- In case of errors, the designer modifies the VHDL code, repeats the analysis and elaboration, and the RTL simulation for checking the system.

# **RTL simulation**

|                                                                                                                                                | R ET                  | INTERPORTED AND AND AND AND AND AND AND AND AND AN |              |              |                |                |              |              |              |     |                | лл         |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------|--------------|--------------|----------------|----------------|--------------|--------------|--------------|-----|----------------|------------|

|                                                                                                                                                | 1<br>240              |                                                    |              |              |                |                | 100          |              |              |     |                |            |

|                                                                                                                                                | 1930                  | - 0055                                             | 1994         | 1981         | 300            | 11612          | 2005         | 2008         | 1002         | 3   | 2012           | LINCE.     |

| <ul> <li>NopAl Australia</li> <li>Pastal Australia</li> <li>Austral Australia</li> <li>Austral Australia</li> <li>Austral Australia</li> </ul> | 0033)<br>0020<br>3314 | 0000                                               | 2004<br>1200 | 1980<br>2001 | >0012<br>>0012 | DX(12<br>20017 | 2009<br>2009 | 1008<br>3008 | 1362<br>0902 |     | 10012<br>20012 | 500<br>300 |

| gg Angel Chappel<br>Chap of Angel<br>Angel Chapter<br>Angel Chapter<br>Angel Chapter<br>Angel Chapter                                          | 211<br>1<br>2         |                                                    |              |              | - TWI          |                | 1 100        |              |              | 100 |                | 0.3000     |

|                                                                                                                                                |                       |                                                    | F            | 7            |                | 1              | 1            | -            | ı.           |     | 1              | 1          |

## **RTL simulation**

- The objective of the VHDL synthesis is that of creating a design that implements the requested functionalities and that meets the designer's constraints in terms of area, speed, etc.

- The VHDL synthesis tools translates an RTL VHDL description into a netlist composed by cells of the target technology.

- Possible errors in this phase are usually due to the use of non-synthesizable constructs.

- At the end of the synthesis process, the synthesizer produces a netlist and a certain number of report files.

- The designer can inspect the netlist, but principally will use the report files for determining the quality of the output synthesis.

- The principal information that we find in these report files is the timing information and area occupation information.

- The area occupation information is used from the designer for determining how many resources are utilized by the design.

- The timing reports provides information about the critical paths.

- The designer can also inspect the netlist, that sometimes may assume the form of a VHDL code.

```

-- Definition of adder

- -

- -

library IEEE, EXEMPLAR; use IEEE.STD LOGIC 1164.all; use

EXEMPLAR.EXEMPLAR 1164.all;

-- Library use clause for technology cells

library altera ;

use altera.all ;

entity adder is

port (

a : IN std logic vector (7 DOWNTO 0) ;

b : IN std logic vector (7 DOWNTO 0) ;

c : OUT std logic vector (7 DOWNTO 0)) ;

end adder ;

architecture test of adder is

component XOR2

port (

Y : OUT std logic ;

IN1 : IN std logic ;

IN2 : IN std logic) ;

end component ;

component LCELL

port (

Y : OUT std logic ;

IN1 : IN std logic) ;

end component ;

component AND2

port (

Y : OUT std logic ;

IN1 : IN std logic ;

IN2 : IN std logic) ;

end component;

•

•

```

```

signal c dup0 7, c dup0 6, c dup0 5, c dup0 4, c dup0 3,

c dup0 2,

c dup0 1, c dup0 0, modgen 0 11 10 c int 7,

modgen 0 11 10 c int 6,

modgen 0 11 10 c int 5, modgen 0 11 10 c int 4,

modgen 0 11 10 c int 3,

modgen 0 11 10 c int 2, modgen 0 11 10 c int 1,

modgen 0 11 10 10 0 10 s1, modgen 0 11 10 10 0 10 s2,

modgen 0 11 10 10 0 10 w1, modgen 0 11 10 10 0 10 w2,

modgen 0 11 10 10 0 10 w3, modgen 0 11 10 10 0 10 w4,

b 2 int, b 1 int, b 0 int, U 0: std logic ;

begin

modgen 0 11 10 10 0 10 sum0 : XOR2 port map ( Y=>

modgen 0 11 10 10 0 10 s1, IN1=>a 0 int, IN2=>U 0);

modgen 0 11 10 10 0 10 sum1 : XOR2 port map ( Y=>

modgen 0 11 10 10 0 10 s2,

IN1=>modgen 0 11 10 10 0 10 s1, IN2=>

b 0 int);

modgen 0 11 10 10 0 10 sum2 : LCELL port map (

Y=>c_dup0_0, IN1=>

modgen 0 11 10 10 0 10 s2);

modgen 0 11 10 10 0 10 c0 : AND2 port map (

Y = > modgen 0 11 10 10 0 10 w1,

IN1=>a 0 int, IN2=>b 0 int);

modgen 0 11 10 10 0 10 c1 : AND2 port map (

\bar{Y} = -modgen 0 11 10 10 0 10 w2,

IN1=>a 0 int, IN2=>U 0);

modgen 0 11 10 10 0 10 c2 : AND2 port map (

\bar{Y} = -modgen 0 11 10 10 0 10 w3,

IN1=>U 0, IN2=>b 0 int);

ix43 : OUTBUF port map ( \OUT\=>c(3), \IN\=>c_dup0_3);

1x44: OUTBUF port map ( OUT = c(2), IN = cdup0(2);

1x45: OUTBUF port map ( OUT = c(1), IN = c dup(1);

1x46 : OUTBUF port map ( OUT = >c(0), IN = >c dup(0);

U 0 XMPLR : GND port map (Y = > U 0);

end test ;

```

```

signal c dup0 7, c dup0 6, c dup0 5, c dup0 4, c dup0 3,

c dup0 2,

c dup0 1, c dup0 0, modgen 0 11 10 c int 7,

modgen 0 11 10 c int 6,

modgen 0 11 10 c int 5, modgen 0 11 10 c int 4,

modgen 0 11 10 c int 3,

modgen 0 11 10 c int 2, modgen 0 11 10 c int 1,

modgen 0 11 10 10 0 10 s1, modgen 0 11 10 10 0 10 s2,

modgen 0 11 10 10 0 10 w1, modgen 0 11 10 10 0 10 w2,

modgen 0 11 10 10 0 10 w3, modgen 0 11 10 10 0 10 w4,

b 2 int, b 1 int, b 0 int, U 0: std logic ;

begin

modgen 0 11 10 10 0 10 sum0 : XOR2 port map ( Y=>

modgen 0 11 10 10 0 10 s1, IN1=>a 0 int, IN2=>U 0);

modgen 0 11 10 10 0 10 sum1 : XOR2 port map ( Y=>

modgen 0 11 10 10 0 10 s2,

IN1=>modgen 0 11 10 10 0 10 s1, IN2=>

b 0 int);

modgen 0 11 10 10 0 10 sum2 : LCELL port map (

Y=>c_dup0_0, IN1=>

modgen 0 11 10 10 0 10 s2);

modgen 0 11 10 10 0 10 c0 : AND2 port map (

Y = > modgen 0 11 10 10 0 10 w1,

IN1=>a 0 int, IN2=>b 0 int);

modgen 0 11 10 10 0 10 c1 : AND2 port map (

\bar{Y} = -modgen 0 11 10 10 0 10 w2,

IN1=>a 0 int, IN2=>U 0);

modgen 0 11 10 10 0 10 c2 : AND2 port map (

\bar{Y} = -modgen 0 11 10 10 0 10 w3,

IN1=>U 0, IN2=>b 0 int);

ix43 : OUTBUF port map ( \OUT\=>c(3), \IN\=>c_dup0_3);

1x44: OUTBUF port map ( OUT = c(2), IN = cdup0(2);

1x45: OUTBUF port map ( OUT = c(1), IN = c dup(1);

1x46 : OUTBUF port map ( OUT = >c(0), IN = >c dup(0);

U 0 XMPLR : GND port map (Y = > U 0);

end test ;

```

## **Gate level functional verification**

- Some designers may want to verify rapidly the synthesis output, to be sure that the synthesized system is correct.

- A part from the case of tool bugs, the synthesized system should provide the same functional behavior of the RTL model.

- For verifying the code, the designer executes the *gate level functional verification*, i.e., he simulates the netlist together with a library of synthesis primitives, using the same test benches of the RTL verification.

- If the simulation provides the same results as before, the synthesis has hopefully not introduced any error; if the results are different, the designer will have to find the reason of the incongruence.

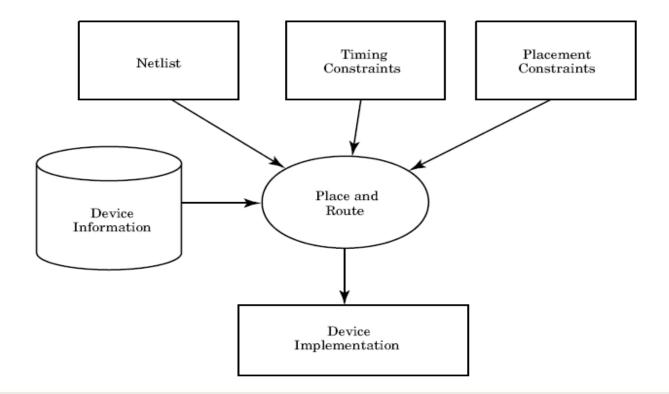

## **Place and routing**

- The place and route tools are used for mapping the synthesized netlist on the target device.

- They place each netlist primitive in an appropriate position on the target device and they route the signals between the primitives for connecting the devices according to the netlist.

- The place and route tools are typically strongly dependent on the device architecture. These tools are developed for taking advantage of every possible architectural or routing benefit allowed by the device.

- The inputs of the place and route operation are the netlist and the timing constraints.

### **Place and routing**

### Post layout timing simulation

- After the place and route process is complete, the designer verifies the result obtained.

- The most common verification method is the gate level post layout timing simulation.

- This simulation combines the netlist used for place and routing, with the timing file obtained from the place and route tool.

- The simulation checks both the functionality and timing performance and verify that the specifications are met.

- Typically, the same test bench of the RTL simulation is used also for the post layout timing simulation.

## Static timing analysis

- For small projects, the simulation is a good method for verifying the functionality and the timing performance of the output system.

- For larger projects, the designer can use the *static timing analysis* for verifying that the timing requirements are met.

- A static timing analyzer traces each path in the design and computes the corresponding propagation delay.

- It outputs a report with the propagation delay of every path or of the most critical paths.

- Douglas L. Perry, «VHDL programming by example» McGraw Hill,

- Chapter 11