#### The processor

## Introduction

- We have seen that the performance of a computer is determined by three key factors:

- instruction count,

- clock cycle time, and

- clock cycles per instruction (CPI).

- The compiler and the instruction set architecture determine the instruction count required for a given program.

- The implementation of the processor determines both the clock cycle time and the number of clock cycles per instruction.

- We can have different organizations of the processor

- Harward or Von Neumann

- And different implementation strategies

- Single cycle; Multi cycle; Pipelined

- We will examine different LEGv8 implementations

- A simplified version (Single cycle)

- A multi cycle version, but for a different processor

- A more realistic pipelined version

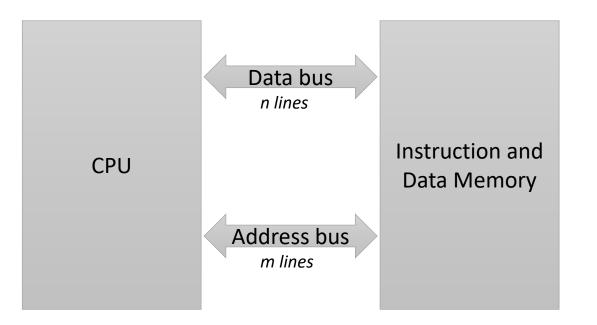

## Von Neumann organization

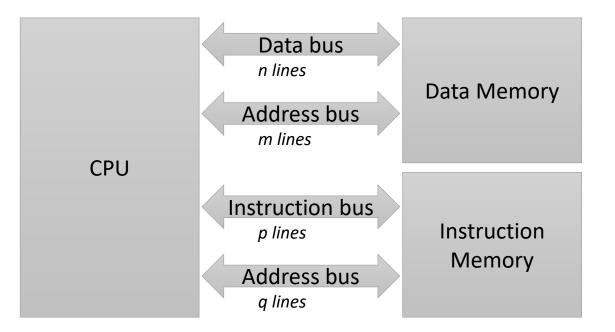

## Harward organization

### **A Basic LEGv8 Implementation**

- We will be examining an implementation that includes a subset of the core LEGv8 instruction set:

- The memory-reference instructions *load register unscaled* (LDUR) and *store register unscaled* (STUR)

- The arithmetic-logical instructions ADD, SUB, AND, and ORR

- The instructions *compare and branch on zero* (**CBZ**) and *branch* (**B**)

- It illustrates the key principles used in creating a datapath and designing the control.

- We will have the opportunity to see

- how the instruction set architecture determines many aspects of the implementation, and

- how the choice of various implementation strategies affects the clock rate and CPI.

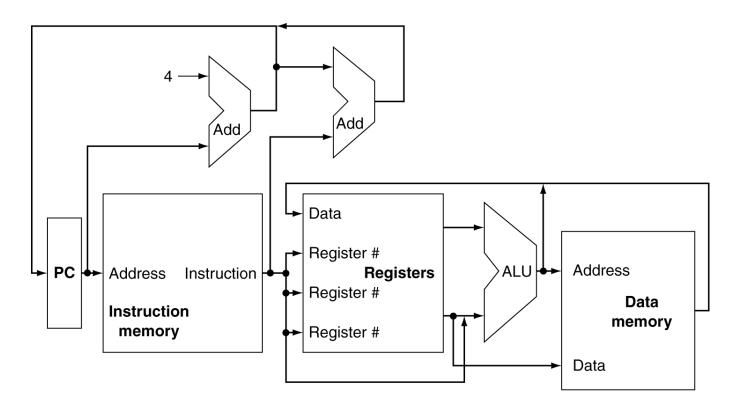

## **Instruction Execution**

- Much of what needs to be done to implement these instructions is the same, independent of the exact class of instruction.

- For every instruction, the first two steps are identical:

- 1. Send the *program counter* (PC) to the memory that contains the code and fetch the instruction from that memory.

- 2. Read one or two registers, using fields of the instruction to select the registers to read.

- After these, the actions required to complete the instruction depend on the instruction class.

- Depending on instruction class

- Use ALU to calculate

- Arithmetic result

- Memory address for load/store

- Comparison with zero in branch

- Access data memory for load/store

- PC ← target address or PC + 4

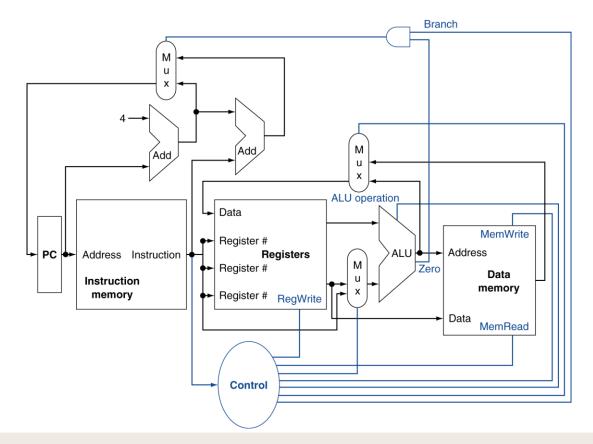

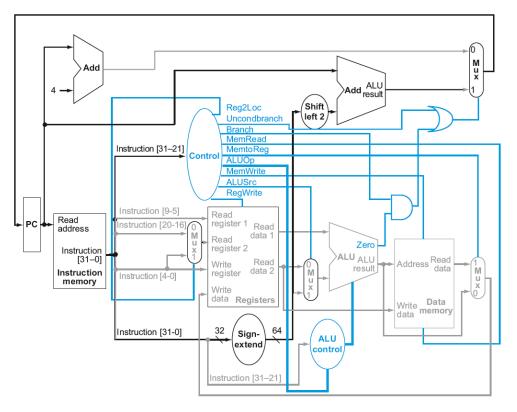

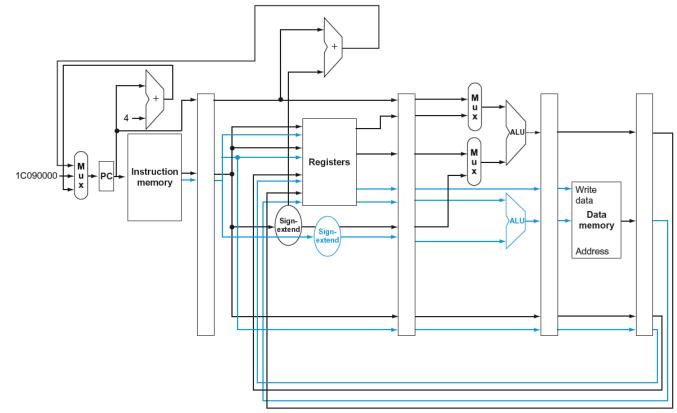

#### **CPU Overview**

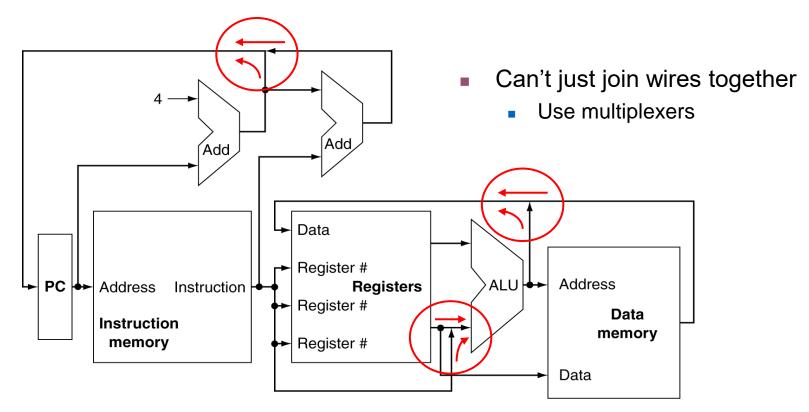

## **Multiplexer**

## Control

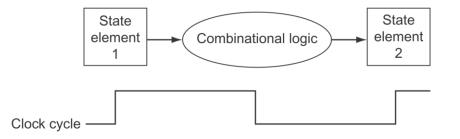

# **Logic Design Conventions**

- The datapath elements in the LEGv8 implementation consist of two different types of logic elements:

- Combinational elements

- Operate on data

- Output is a function of input

- State (sequential) elements

- Store information

- E.g, registers and memories

- We call these elements **state elements** because, if we pulled the power plug on the computer, we could restart it accurately by loading the state elements with the values they contained before we pulled the plug.

- A state element has at least two inputs and one output:

- Data input, clock.

- The output is the value that was written in an earlier clock cycle.

- The clock is used to determine when the state element should be written.

# **Clocking Methodology**

- A clocking methodology defines when signals can be read and when they can be written.

- We will assume an **edge-triggered** clocking methodology.

- Any values stored in a sequential logic element are updated only on a clock edge.

- All signals must propagate from state element 1, through the combinational logic, and to state element 2 in the time of one clock cycle.

- The time necessary for the signals to reach state element 2 defines the length of the clock cycle.

- If a state element is not updated on every clock, then an explicit write **control signal** is required.

- The state element is changed only when the control signal is **asserted** and a clock edge occurs.

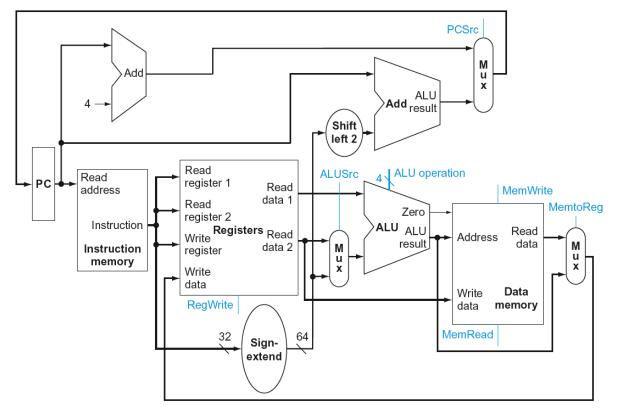

## **The Simple Datapath**

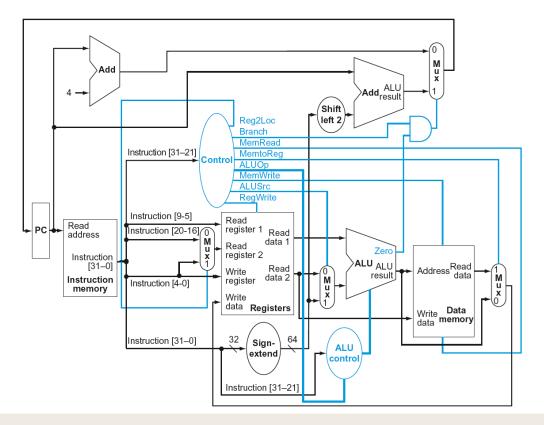

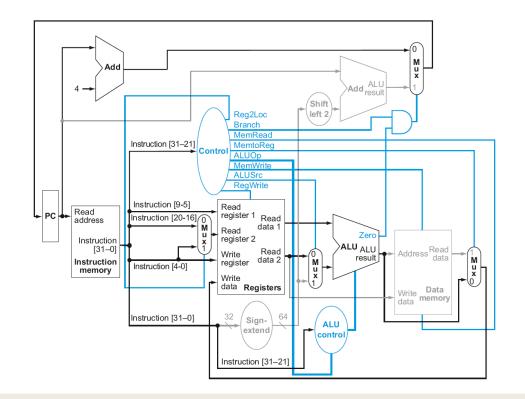

#### The Simple Datapath with Control

## **ALU Control**

| ALU control lines | Function     |

|-------------------|--------------|

| 0000              | AND          |

| 0001              | OR           |

| 0010              | add          |

| 0110              | subtract     |

| 0111              | pass input b |

| 1100              | NOR          |

- ALU used for

- Load/Store: F = add

- Branch: F = compare

- R-type: F depends on opcode

- Assume 2-bit ALUOp derived from opcode:

- 00 add 00 for loads and stores,

- 01 pass input b for CBZ, or

- 10 determined by opcode field for R-type

| Instruction | ALUOp | Instruction<br>operation      | Opcode field | Desired<br>ALU action | ALU control<br>Input |

|-------------|-------|-------------------------------|--------------|-----------------------|----------------------|

| LDUR        | 00    | load register                 | XXXXXXXXXXXX | add                   | 0010                 |

| STUR        | 00    | store register                | XXXXXXXXXXXX | add                   | 0010                 |

| CBZ         | 01    | compare and<br>branch on zero | XXXXXXXXXXXX | pass input b          | 0111                 |

| R-type      | 10    | ADD                           | 10001011000  | add                   | 0010                 |

| R-type      | 10    | SUB                           | 11001011000  | subtract              | 0110                 |

| R-type      | 10    | AND                           | 10001010000  | AND                   | 0000                 |

| R-type      | 10    | ORR                           | 10101010000  | OR                    | 0001                 |

# **Instruction format**

• We will see the implementation of three instructions:

ADD X1, X2, X3 LDUR X1, [X2, offset] CBZ X1, offset

| Field            | opcode             | Rm      | shar | nt    | Rn  | Rd  |

|------------------|--------------------|---------|------|-------|-----|-----|

| Bit positions    | 31:21              | 20:16   | 15:1 | LO    | 9:5 | 4:0 |

| a. R-type instru | ction              |         |      |       |     |     |

|                  |                    |         |      |       |     |     |

| Field            | 1986 or 1984       | addres  | S    | 0     | Rn  | Rt  |

| Bit positions    | 31:21              | 20:12   |      | 11:10 | 9:5 | 4:0 |

| b. Load or store | e instruction      |         |      |       |     |     |

|                  |                    |         |      |       |     |     |

| Field            | 180                | address |      |       |     | Rt  |

| Bit positions    | 31:24              | 23:5    |      |       |     | 4:0 |

| c. Conditional h | aranch instruction |         |      |       |     |     |

c. Conditional branch instruction

## **Instruction format**

- There are several major observations about this instruction format that we will rely on:

- The opcode field is between 6 and 11 bits wide and found in bits 31:26 to 31:21.

- The first register operand is always in bit positions 9:5 (Rn) for both R-type instructions and for the base register for load and store instructions.

- The other register operand is in one of two places. It is in bit positions 20:16 (Rm) for R-type instructions and it is in bit positions 4:0 (Rt) for the register to be written by a load. That is also the field that specifies the register to be tested for zero for compare and branch on zero.

- Another operand can also be a 19-bit offset for compare and branch on zero or a 9-bit offset for load and store.

- The destination register for R-type instructions (Rd) and for loads (Rt) is in bit positions 4:0.

## ADD X1, X2, X3

- Although everything occurs in one clock cycle, we can think of four steps to execute the instruction;

- these steps are ordered by the flow of information:

- 1. The instruction is fetched, and the PC is incremented.

- 2. Two registers, X2 and X3, are read from the register file; also, the main control unit computes the setting of the control lines during this step.

- 3. The ALU operates on the data read from the register file, using portions of the opcode to generate the ALU function.

- 4. The result from the ALU is written into the destination register (X1) in the register file.

#### ADD X1, X2, X3

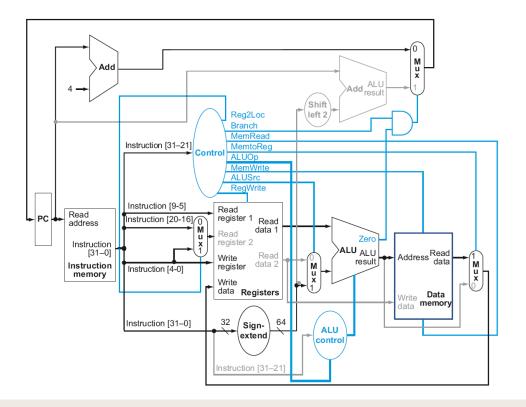

# LDUR X1, [X2,offset]

- We can think of a load instruction as operating in five steps :

- 1. An instruction is fetched from the instruction memory, and the PC is incremented.

- 2. A register (X2) value is read from the register file.

- 3. The ALU computes the sum of the value read from the register file and the sign-extended 9 bits of the instruction (offset).

- 4. The sum from the ALU is used as the address for the data memory.

- 5. The data from the memory unit is written into the register file (X1).

# LDUR X1, [X2,offset]

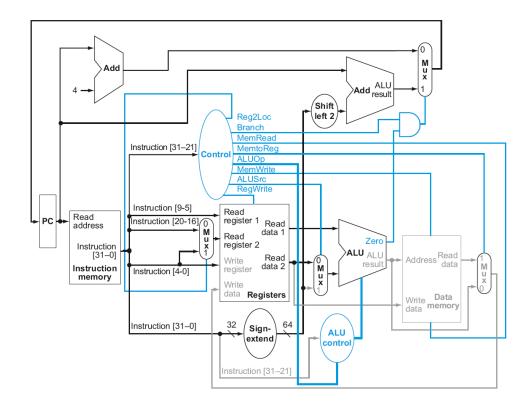

## CBZ X1, offset

- It operates much like an R-format instruction, but the ALU output is used to determine whether the PC is written with PC + 4 or the branch target address.

- We can think of four steps in the execution:

- 1. An instruction is fetched from the instruction memory, and the PC is incremented.

- 2. The register X1 is read from the register file using bits 4:0 of the instruction (Rt).

- 3. The ALU passes the data value read from the register file. The value of PC is added to the signextended, 19 bits of the instruction (offset) are shifted left by two; the result is the branch target address.

- 4. The Zero status information from the ALU is used to decide which adder result to store in the PC.

## CBZ X1, offset

## **Unconditional Branch**

# Why a Single-Cycle Implementation is not Used Today

- Although the single-cycle design will work correctly, it is too inefficient to be used in modern designs.

- Notice that the clock cycle must have the same length for every instruction in this single-cycle design.

- The longest possible path in the processor determines the clock cycle.

- This path is most likely a load instruction, which uses five functional units in series:

- the instruction memory, the register file, the ALU, the data memory, and the register file.

- Although the CPI is 1, the overall performance of a single-cycle implementation is likely to be poor, since the clock cycle is too long.

- Historically, early computers with very simple instruction sets did use this implementation technique.

- However, if we tried to implement the floating-point unit or an instruction set with more complex instructions, this single-cycle design wouldn't work well at all.

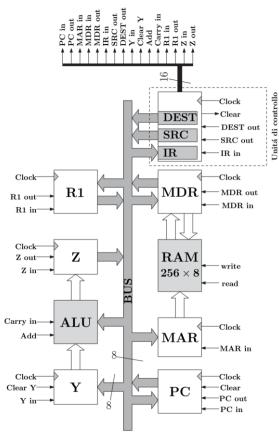

## **Multi-cycle Control strategies**

$R1 \leftarrow R1 + M[num]$

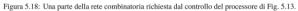

Figura 5.13: Un ipotetico processore a 8 bit.

## **Multi-cycle Control strategies**

- Let us consider the hypothetical processor of the previous slide.

- The control unit decode and execute the instructions, and update the program counter (PC), fetching the next instruction.

- The control unit is here composed of three register:

- IR has the OpCode of the instruction

- SRC can contain a parameter included in the IW or a memory address, often expressed in relative terms as a PC increment.

- DEST can contain an address or the pointer to a register where to write the result.

- From the analysis of the OpCode, the control unit must provide the sequence of control signals necessary for

- 1. Fetch and update of the PC

- 2. Execution of the current instruction.

## **Multi-cycle Control strategies**

- Historically, two possible approaches have been followed for the control unit:

- *Microprogrammed* approach

- *Cabled* approach

- Microcontrollers with old architectures are microprogrammed. More recent ones, especially RISC ones, are cabled.

- Two possible clocking strategies:

- Multi-cycle control

- Fetch, decode, execute performed with multiple clock periods.

- Single-cycle control

- Fetch, decode, execute performed in a single period.

- Single-cycle control strategy is employed only in cabled controls.

- Multi-cycle control strategy is used both in all microprogrammed controls and in some cabled controls.

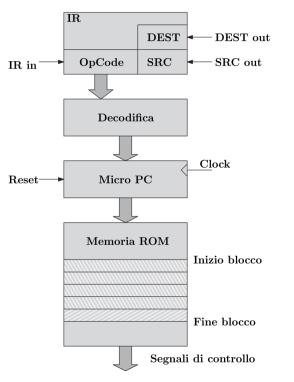

## **Microprogrammed control**

- Is implemented with a control unit that replicates the structure of a simple CPU with a memory, a PC, an ALU, called **microcode engine**.

- Each macro-instruction corresponds to a microcode, composed by some words. Microcodes are stored in a ROM memory.

- Two possibilities:

- *Horizontal microprogramming*: the control unit execute the code strictly sequentially, starting from the address pointed by the OpCode.

- *Vertical microprogramming*: jumps are possible and allow to repeat microcode segments, i.e., the introduction of micro-subroutines.

- The *microcode* is composed of words, whose bits directly assert/negate specific control signals.

- The microcode *wordlenght* depends on the number of control signals.

# **Microprogrammed control**

Figura 5.14: Schema a blocchi semplificato di una unità di controllo microprogrammata.

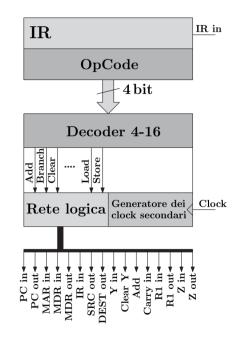

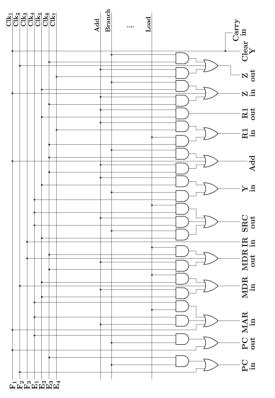

- The microcode engine is replaced by a *combinatorial logic circuit* that generates directly the control signals form the OpCode of the current instruction, managing also temporizations.

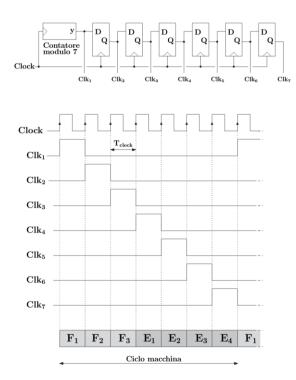

- Includes a *secondary clock generator*, whose purpose is the time distribution of control signal activations.

- Let us assume that a single instruction is executed in 7 periods.

- The secondary clock generator is a clock divider by 7 that generates 1 pulse every 7 clock periods, and feeds a shift register of 6 FlipFlops.

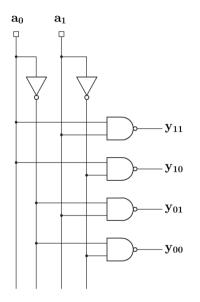

- The decoder activates one output line for each OpCode.

- The combinatorial network, composed by AND and OR gates, feeds the control lines on the basis of the OpCode and of secondary clock state (from 1 to 7).

- The solution provides *very fast response*, with *little silicon area occupation*, but *lack flexibility*, and could require *nop* cycles to manage shorter instructions.

Figura 5.15: Unità di controllo cablata: è visibile un decodificatore delle istruzioni (a 4 bit), un generatore dei clock secondari e una rete logica combinatoria che asserisce i segnali di controllo del processore, elaborando sia i clock secondari che le linee del bus gestito dal decodificatore.

Figura 5.16: Circuito per la generazione dei segnali di clock secondari richiesti da una unità di controllo cablata.

#### Example

Figura 5.17: Schema di principio di un decodificatore binario, o demultiplexer, a 2 bit. Ciascuna delle 4 combinazioni di ingresso attiva, portandola, in questo caso, a livello logico *basso*, una e una sola delle 4 uscite.

## **Multi-cycle vs Single-cycle Organization**

- Only the availability of multiple resources allow a single cycle temporization.

- It requires at least that the fetch phase is performed simultaneously to decode and execute.

- It imposes the following system requirements:

- Separate data memory and instruction memory;

- Separate ALU for PC increment;

- Flexible PC increment for managing jumps without main ALU intervention.

- Unless the instruction set is very simple, the single cycle organization is often *inefficient*. It is the most onerous instruction that determine the clock period.

- On the contrary, in multi-cycle organization, it is the slowest functional unit (ALU or memory) that determines the minimum period.

- It is possible to combine advantages of both, using a *pipeline* organization.

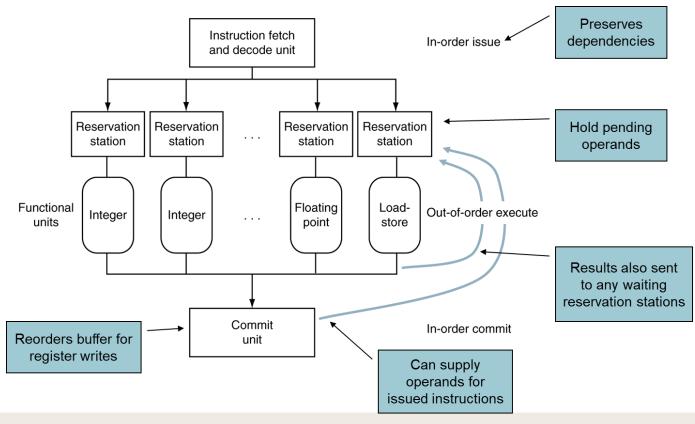

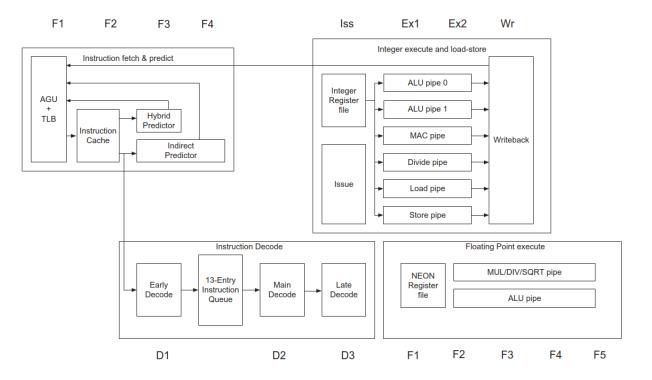

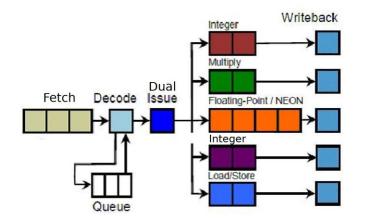

## **An Overview of Pipelining**

- **Pipelining** is an implementation technique in which multiple instructions are overlapped in execution.

- Today, pipelining is nearly universal.

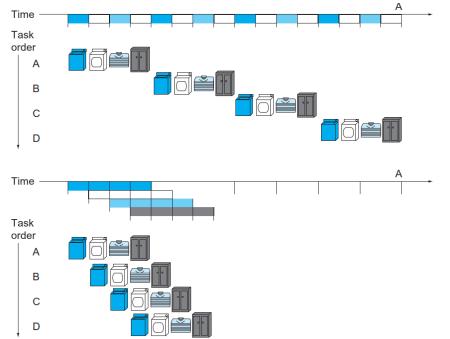

# **Pipelining analogy**

- Pipelined laundry overlapping execution

- Parallelism improves performance

- Four loads:

- Speedup

= 16/7 = 2.3

- Non-stop:

- Speedup =  $4n/1n + 3 \approx 4$

- = number of stages

- The pipelining paradox is that the time for processing a single laundry load is not shorter for pipelining.

- But more loads are process per hour.

- Pipelining improves throughput of our laundry system.

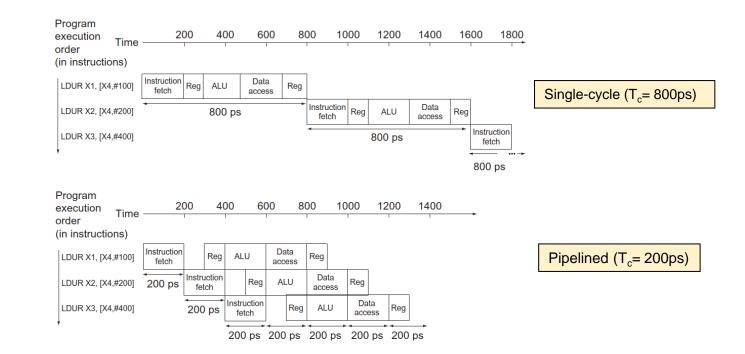

## **Single-Cycle versus Pipelined Performance**

- LEGv8 instructions classically take five steps:

- 1. Fetch instruction from memory.

- 2. Read registers and decode the instruction.

- 3. Execute the operation or calculate an address.

- 4. Access an operand in data memory (if necessary).

- 5. Write the result into a register (if necessary).

- Hence, the LEGv8 pipeline we consider has five stages.

## **Single-Cycle versus Pipelined Performance**

- We limit our attention to seven instructions: load register (LDUR), store register (STUR), add (ADD), subtract (SUB), AND (AND), OR (ORR), and compare and branch on zero (CBZ).

- Assume time for stages is

- 100ps for register read or write

- 200ps for other stages

| Instruction class             | Instruction<br>fetch | Register<br>read | ALU<br>operation | Data<br>access | Register<br>write | Total<br>time |

|-------------------------------|----------------------|------------------|------------------|----------------|-------------------|---------------|

| Load register (LDUR)          | 200 ps               | 100 ps           | 200 ps           | 200 ps         | 100 ps            | 800 ps        |

| Store register (STUR)         | 200 ps               | 100 ps           | 200 ps           | 200 ps         |                   | 700 ps        |

| R-format (ADD, SUB, AND, ORR) | 200 ps               | 100 ps           | 200 ps           |                | 100 ps            | 600 ps        |

| Branch (CBZ)                  | 200 ps               | 100 ps           | 200 ps           |                |                   | 500 ps        |

## **Single-Cycle versus Pipelined Performance**

## **Pipeline Speedup**

• If the stages are perfectly balanced, then

$\text{Time between instructions}_{\text{pipelined}} = \frac{\text{Time between instructions}_{\text{nonpipelined}}}{\text{Number of pipe stages}}$

- Under ideal conditions and with a large number of instructions, the speed-up from pipelining is approximately equal to the number of pipeline stages.

- If the stages are not balanced, the speedup is less.

- Moreover, we will see pipelining involves some overhead.

- In reality, in our case the total execution time for the three instructions is 1400 ps versus 2400 ps.

- But if we add 1,000,000 instructions:

$$\frac{800,002,400 \text{ ps}}{200,001,400 \text{ ps}} \simeq \frac{800 \text{ ps}}{200 \text{ qs}} \simeq 4.00$$

• Pipelining improves performance by *increasing instruction throughput, in contrast to decreasing the execution time of an individual instruction.*

## **Designing Instruction Sets for Pipelining**

- LEGv8 was designed for pipelined execution:

- All instructions are 32-bits

- Easier to fetch and decode in one cycle

- c.f. x86: 1- to 17-byte instructions

- Few and regular instruction formats

- Can decode and read registers in one step

- Memory operands only appear in loads or stores

- We can use the execute stage to calculate the memory address and then access memory in the following stage

### **Pipeline Hazards**

- There are situations in pipelining when the next instruction cannot execute in the following clock cycle.

- These events are called **hazards**, and there are three different types:

- Structure hazards

- When a planned instruction cannot execute in the proper clock cycle because the hardware does not support the combination of instructions that are set to execute.

- Data hazard

- When a planned instruction cannot execute in the proper clock cycle because data that are needed to execute the instruction are not yet available.

- Control hazard, also called branch hazard

- When the proper instruction cannot execute in the proper pipeline clock cycle because the instruction that was fetched is not the one that is needed; that is, the flow of instruction addresses is not what the pipeline expected.

#### **Structural Hazards**

- When a planned instruction cannot execute in the proper clock cycle because the hardware does not support the combination of instructions that are set to execute.

- The LEGv8 instruction set was designed to be pipelined, making it fairly easy for designers to avoid structural hazards when designing a pipeline.

- Suppose, however, that we had a single memory instead of two.

- Load/store requires data access

- Instruction fetch would have to *stall* for that cycle

- Would cause a pipeline "bubble"

- Hence, pipelined datapaths require separate instruction/data memories

- Or separate instruction/data caches

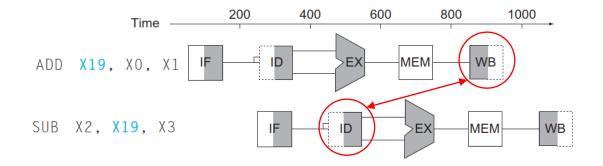

#### **Data Hazards**

- Data hazards arise from the dependence of one instruction on an earlier one that is still in the pipeline.

- For example:

ADD X19, X0, X1 SUB X2, X19, X3

## Forwarding (aka Bypassing)

- We could try to rely on compilers to remove all such hazards, but the results would not be satisfactory: these dependences happen just too often.

- The primary solution is based on **forwarding**:

- As soon as the ALU creates the sum for the add, we can supply it as an input for the subtract.

- Requires extra connections in the datapath

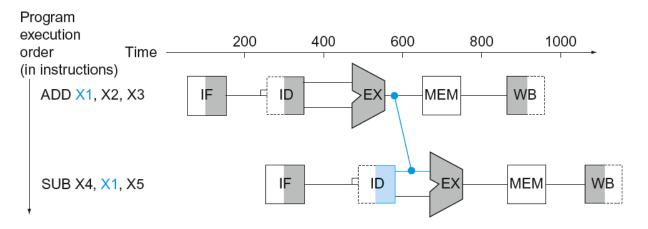

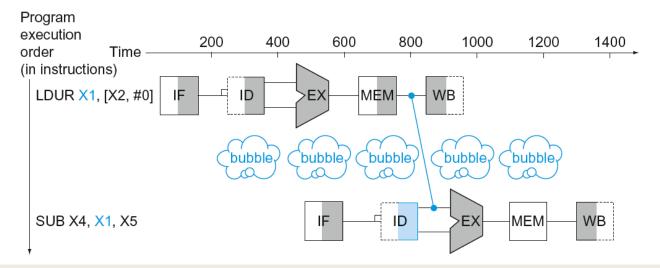

### Load-Use Data Hazard

- Forwarding cannot prevent all pipeline stalls.

- Suppose the first instruction was a load of X1 instead of an add.

- The desired data would be available only after the *fourth stage* of the first instruction in the dependence, which is *too late for* the input of *the third stage* of SUB.

#### Load-Use Data Hazard

- **load-use data hazard** A specific form of data hazard in which the data being loaded by a load instruction have not yet become available when they are needed by another instruction.

- **pipeline stall** Also called **bubble**. A stall initiated in order to resolve a hazard.

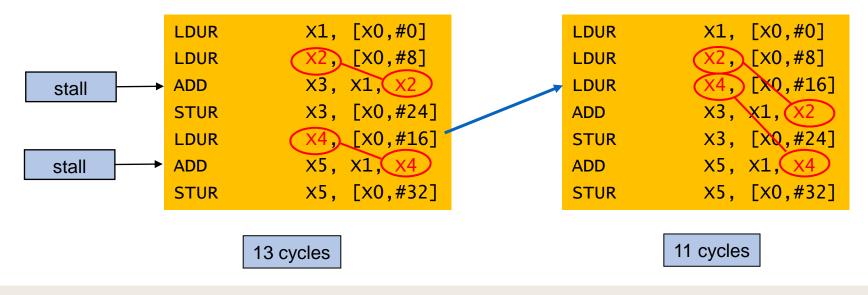

## **Reordering Code to Avoid Pipeline Stalls**

- We can prevent Load-Use Data Hazard by reordering the code to avoid the use of the load result in the next instruction.

- C code for A = B + E; C = B + F;

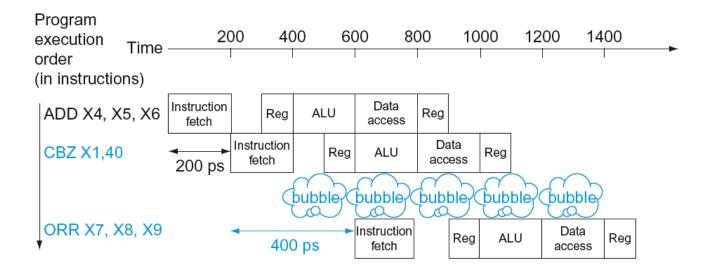

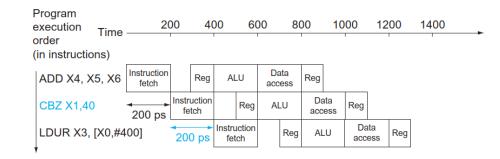

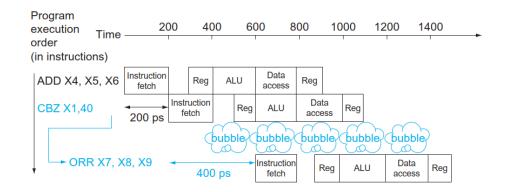

#### **Control Hazards**

- **Control hazard** also called **branch hazard**. When the proper instruction cannot execute in the proper pipeline clock cycle because the instruction that was fetched is not the one that is needed; that is, the flow of instruction addresses is not what the pipeline expected.

- In the **conditional branch instruction**, we must begin fetching the instruction following the branch on the following clock cycle....

- Nevertheless, *the pipeline cannot possibly know what the next instruction should be*, since it only just received the branch instruction from memory!

- In LEGv8 pipeline:

- We need to compare registers and compute the target early in the pipeline.

- Let's assume that we put in enough extra hardware so that we can test a register, calculate the branch address, and update the PC during the second stage of the pipeline (ID stage).

### **Stall on Branch**

• One possible solution is to stall immediately after we fetch a branch, waiting until the pipeline determines the outcome of the branch.

### Performance of "Stall on Branch"

- Estimate the impact on the clock cycles per instruction (CPI) of stalling on branches.

- Assume all other instructions have a CPI of 1.

- Conditional branches are 17% of the instructions executed in SPECint2006.

- Since the other instructions (83%) run have a CPI of 1, and conditional branches took one extra clock cycle for the stall, then we would see a CPI of

CPI = 0.83\*1+0.17\*2 = 1.17

• Hence a slowdown of 1.17 versus the ideal case.

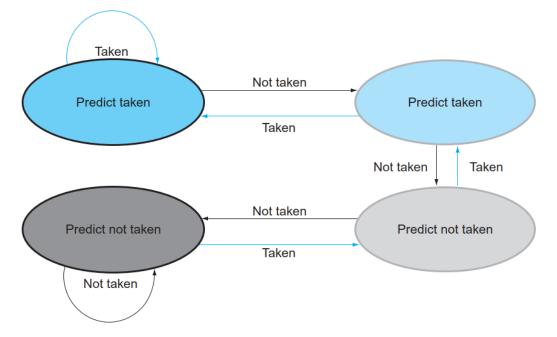

#### **Branch Prediction**

- If we cannot resolve the branch in the second stage, as is often the case for *longer pipelines*, then we'd see an *even larger slowdown* if we stall on conditional branches.

- The cost of this option is too high for most computers to use and motivates a second solution to the control hazard: **predict** the outcome of branch.

- This option does not slow down the pipeline when you are correct.

- When you are wrong: you need to redo the load that was washed while guessing the decision (with the creation of a **bubble**).

- One simple approach is to predict always that conditional branches will be untaken.

- When you're right, the pipeline proceeds at full speed.

- Only when conditional branches are taken does the pipeline stall.

#### **Branch Prediction**

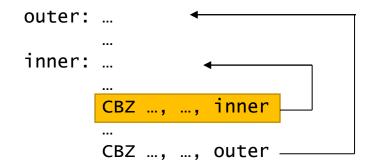

### **More-Realistic Branch Prediction**

- A more sophisticated version of **branch prediction** would have some conditional branches predicted as taken and some as untaken.

- Static branch prediction

- Based on typical branch behavior

- Example: loop and if-statement branches

- Predict backward branches taken

- Predict forward branches not taken

- **Dynamic** branch prediction

- Hardware measures actual branch behavior

- e.g., record recent history of each branch

- Assume future behavior will continue the trend

- When wrong, stall while re-fetching, and update history

## Third approach: delayed branch

- There is a third approach to the control hazard, called a *delayed branch*.

- Used in MIPS, TI C54, and many other processors

- The delayed branch *always executes the next sequential instruction*, with the branch taking place after that one instruction delay.

- It is hidden from the MIPS assembly language programmer because the assembler can automatically arrange the instructions to get the branch behavior desired by the programmer.

- MIPS software will place an instruction immediately after the delayed branch instruction that is not affected by the branch.

- A taken branch changes the address of the instruction that follows this safe instruction.

### **Pipeline Summary: the BIG picture**

- Pipelining increases the number of simultaneously executing instructions and the rate at which instructions are started and completed.

- Pipelining does not reduce the time it takes to complete an individual instruction, i.e., the *latency*.

- For example, the five-stage pipeline still takes five clock cycles for the instruction to complete.

- Pipelining *improves instruction throughput* rather than individual instruction execution time.

- Instruction sets can either make life harder or simpler for pipeline designers, who must already cope with *structural, control, and data hazards*.

- Branch prediction and forwarding help make a computer fast while still getting the right answers.

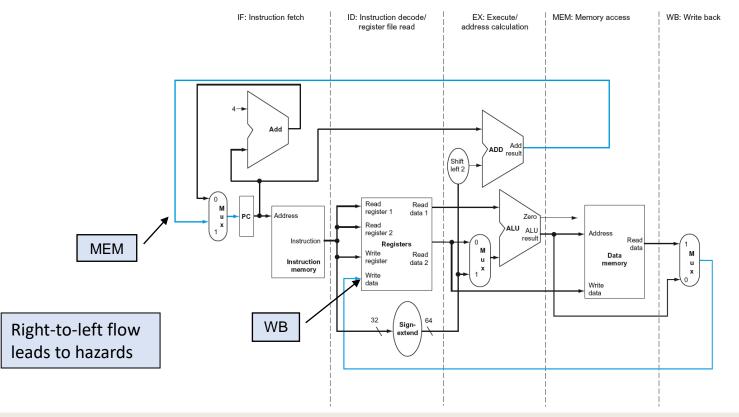

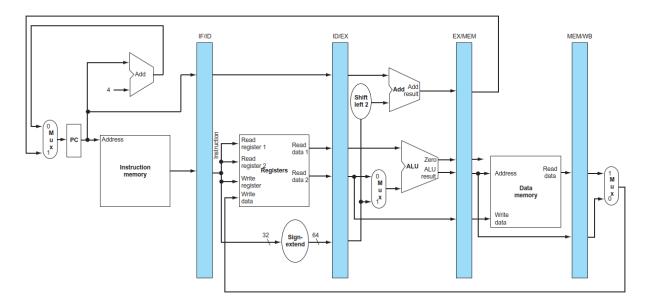

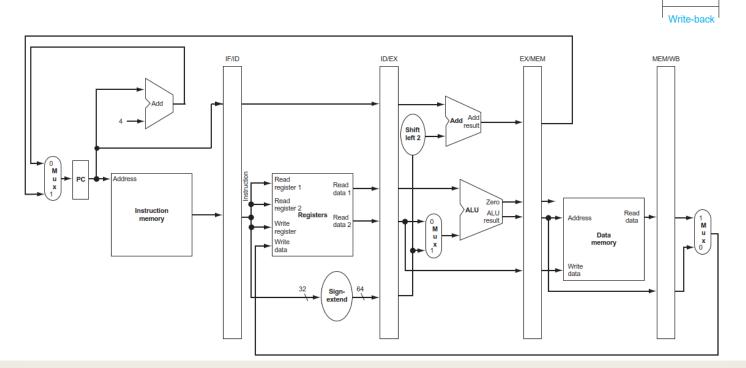

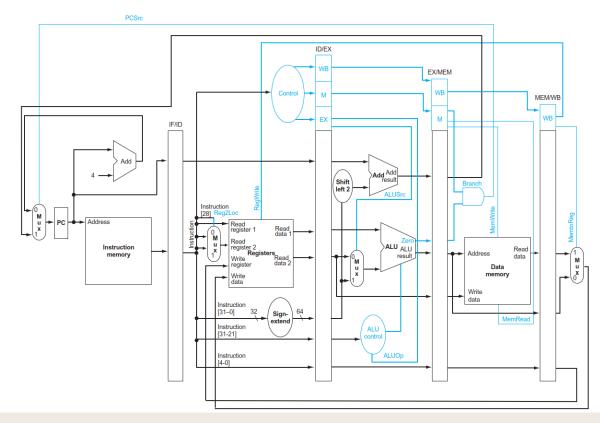

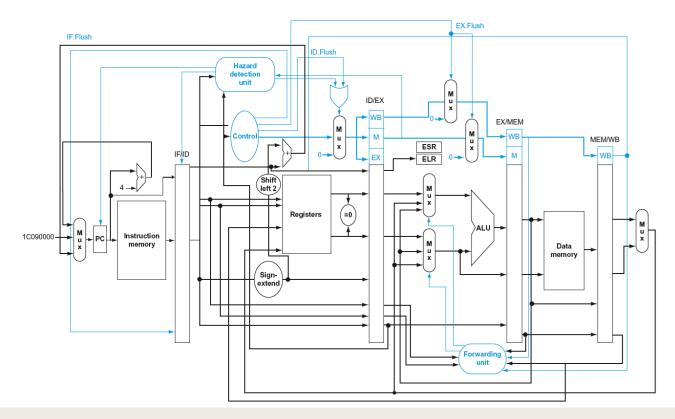

## **LEGv8 Pipelined Datapath**

### **Pipeline registers**

- Need registers between stages

- To hold information produced in previous cycle

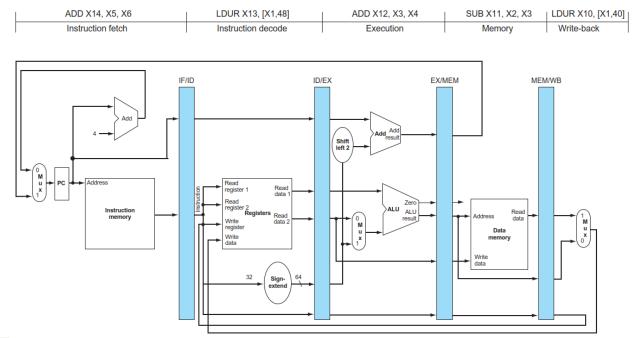

## **Pipeline Operation**

- Cycle-by-cycle flow of instructions through the pipelined datapath

- "Single-clock-cycle" pipeline diagram

- Shows pipeline usage in a single cycle

- Highlight resources used

- c.f. "multi-clock-cycle" diagram

- Graph of operation over time

- We'll look at "single-clock-cycle" diagrams for load & store

## IF for Load, Store, ...

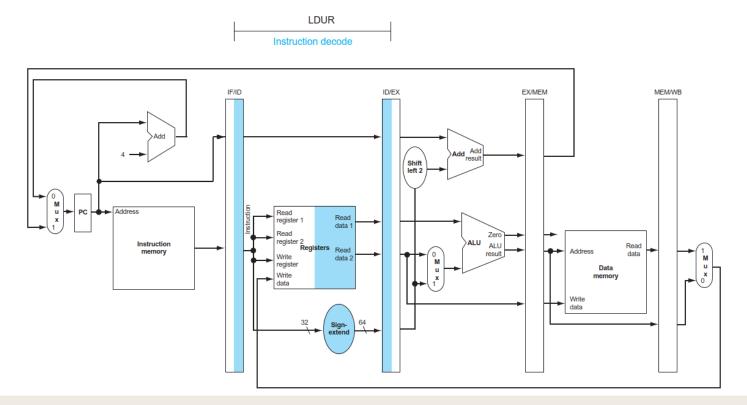

## ID for Load, Store, ...

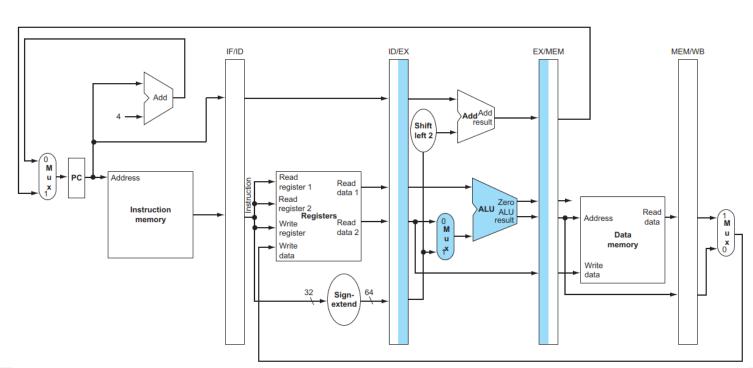

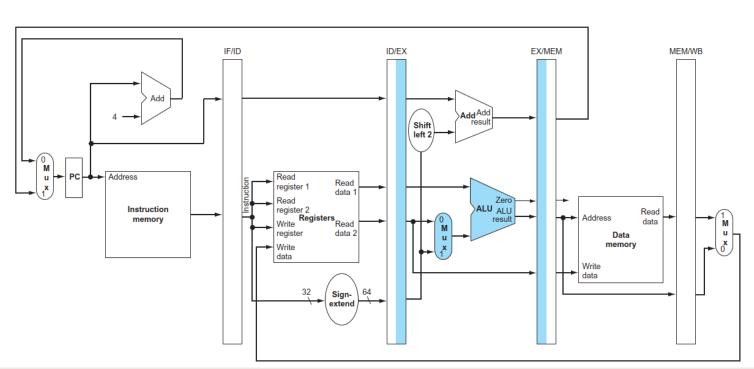

## **EX for Load**

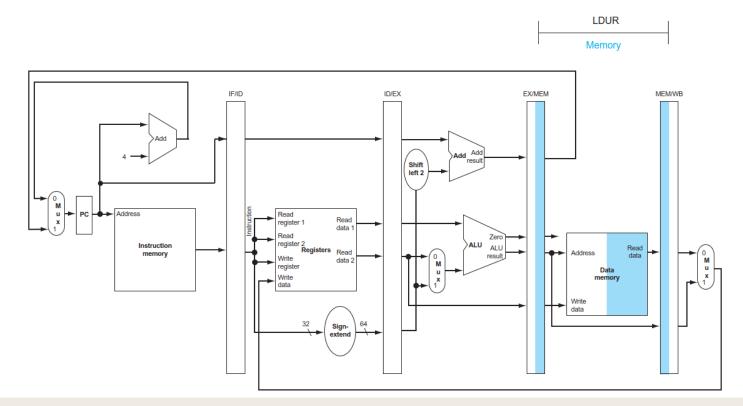

## **MEM for Load**

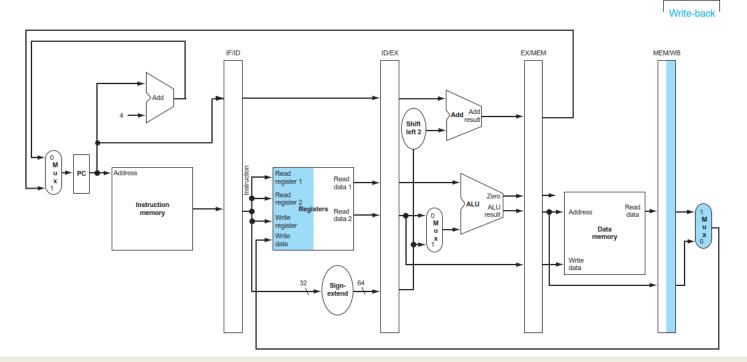

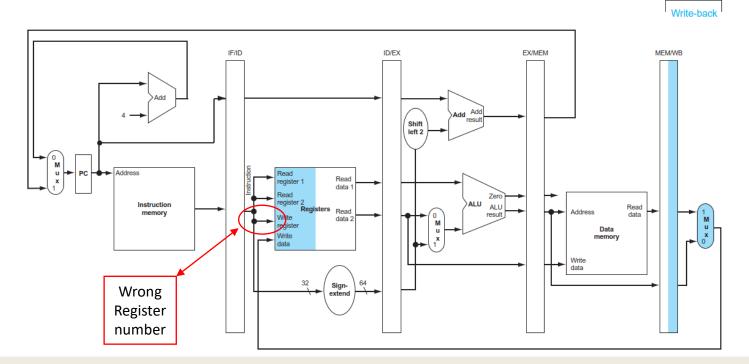

### WB for Load

A. Carini – Digital System Architectures

LDUR

### WB for Load

UNIVERSITÀ DEGLI STUDI DI TRIESTE

A. Carini – Digital System Architectures

LDUR

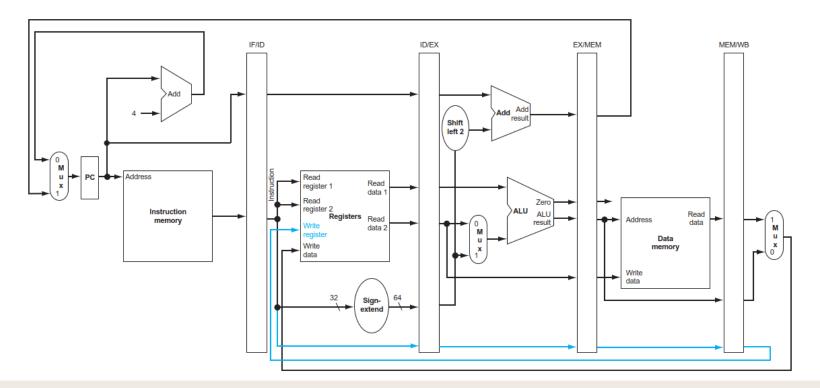

#### **Corrected Datapath for Load**

### **EX for Store**

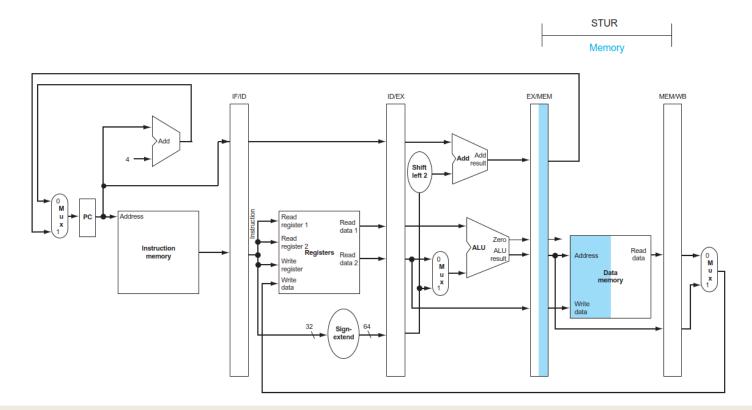

## **MEM for Store**

### **WB for Store**

A. Carini – Digital System Architectures

STUR

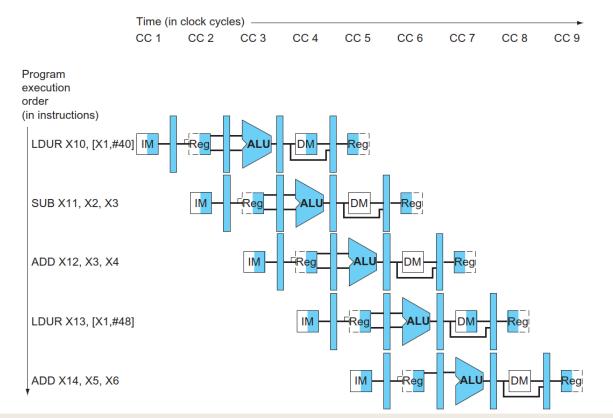

#### Multi-Cycle Pipeline Diagram

## Multi-Cycle Pipeline Diagram

• Traditional form:

|                    | Time (in clock cycles)                                                         |                                                                                                                                                              |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|--------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                    | CC 1                                                                           | CC 2                                                                                                                                                         | CC 3                                                                                                                                                                                                            | CC 4                                                                                                                                                                                                                                                                                                                           | CC 5                                                                                                                                                                                                                                                                                                                                                                                                       | CC 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CC 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CC 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CC 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| xecution<br>rder   |                                                                                |                                                                                                                                                              |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| LDUR X10, [X1,#40] | Instruction<br>fetch                                                           | Instruction decode                                                                                                                                           | Execution                                                                                                                                                                                                       | Data<br>access                                                                                                                                                                                                                                                                                                                 | Write-back                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| SUB X11, X2, X3    |                                                                                | Instruction<br>fetch                                                                                                                                         | Instruction decode                                                                                                                                                                                              | Execution                                                                                                                                                                                                                                                                                                                      | Data<br>access                                                                                                                                                                                                                                                                                                                                                                                             | Write-back                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| ADD X12, X3, X4    |                                                                                |                                                                                                                                                              | Instruction<br>fetch                                                                                                                                                                                            | Instruction decode                                                                                                                                                                                                                                                                                                             | Execution                                                                                                                                                                                                                                                                                                                                                                                                  | Data<br>access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Write-back                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| LDUR X13, [X1,#48] |                                                                                |                                                                                                                                                              |                                                                                                                                                                                                                 | Instruction<br>fetch                                                                                                                                                                                                                                                                                                           | Instruction<br>decode                                                                                                                                                                                                                                                                                                                                                                                      | Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Data<br>access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Write-back                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| ADD X14, X5, X6    |                                                                                |                                                                                                                                                              |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                | Instruction<br>fetch                                                                                                                                                                                                                                                                                                                                                                                       | Instruction decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Data<br>access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Write-back                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                    | LDUR X10, [X1,#40]<br>SUB X11, X2, X3<br>ADD X12, X3, X4<br>LDUR X13, [X1,#48] | CC 1<br>rogram<br>xecution<br>rder<br>n instructions)<br>LDUR X10, [X1,#40] Instruction<br>fetch<br>SUB X11, X2, X3<br>ADD X12, X3, X4<br>LDUR X13, [X1,#48] | CC 1     CC 2       Program     xecution       rder     ninstructions)       LDUR X10, [X1,#40]     Instruction decode       SUB X11, X2, X3     Instruction fetch       ADD X12, X3, X4     LDUR X13, [X1,#48] | CC 1     CC 2     CC 3       Program xecution rder n instructions)     Instruction Instruction decode     Execution       LDUR X10, [X1,#40]     Instruction fetch     Instruction decode       SUB X11, X2, X3     Instruction fetch     Instruction decode       ADD X12, X3, X4     Instruction fetch     Instruction fetch | CC 1     CC 2     CC 3     CC 4       Program xecution rder n instructions)     Instruction Instruction decode     Execution     Data access       LDUR X10, [X1,#40]     Instruction fetch     Instruction decode     Execution       SUB X11, X2, X3     Instruction fetch     Instruction decode     Execution       ADD X12, X3, X4     Instruction fetch     Instruction decode     Instruction fetch | CC 1     CC 2     CC 3     CC 4     CC 5       rogram<br>xecution<br>rder<br>n instructions)     Instruction<br>fetch     Instruction<br>decode     Data<br>access     Write-back       LDUR X10, [X1,#40]     Instruction<br>fetch     Instruction<br>decode     Execution     Data<br>access     Write-back       SUB X11, X2, X3     Instruction<br>fetch     Instruction<br>decode     Execution     Data<br>access       ADD X12, X3, X4     Instruction<br>fetch     Instruction<br>decode     Execution       LDUR X13, [X1,#48]     Instruction<br>fetch     Instruction<br>decode     Instruction<br>Instruction | CC 1       CC 2       CC 3       CC 4       CC 5       CC 6         rogram xecution rder n instructions)       Instruction Instruction decode       Execution       Data access       Write-back         SUB X10, [X1,#40]       Instruction fetch       Instruction decode       Execution       Data access       Write-back         SUB X11, X2, X3       Instruction fetch       Instruction decode       Execution       Data access       Write-back         ADD X12, X3, X4       Instruction fetch       Instruction linstruction decode       Execution       Data access         LDUR X13, [X1,#48]       Instruction fetch       Instruction linstruction decode       Execution       Data access         ADD X14, X5, X6       Instruction instruction fetch       Instruction linstruction       Execution | CC 1       CC 2       CC 3       CC 4       CC 5       CC 6       CC 7         rogram xecution rder n instructions)       Instruction Instruction decode       Execution       Data access       Write-back         SUB X10, [X1,#40]       Instruction fetch       Instruction Instruction decode       Execution       Data access       Write-back         SUB X11, X2, X3       Instruction fetch       Instruction decode       Execution       Data access       Write-back         ADD X12, X3, X4       Instruction fetch       Instruction decode       Execution       Data access       Write-back         LDUR X13, [X1,#48]       Instruction fetch       Instruction decode       Execution       Data access         ADD X14, X5, X6       Instruction Instruction fetch       Instruction Instruction fetch       Execution       Data access | CC 1       CC 2       CC 3       CC 4       CC 5       CC 6       CC 7       CC 8         rogram xecution rder n instructions)       Instruction Instruction decode       Execution Data access       Write-back         LDUR X10, [X1,#40]       Instruction decode       Execution access       Write-back         SUB X11, X2, X3       Instruction Instruction decode       Execution access       Write-back         ADD X12, X3, X4       Instruction fetch       Instruction linstruction decode       Execution access       Write-back         LDUR X13, [X1,#48]       Instruction instruction fetch       Instruction instruction access       Write-back       Data access       Write-back         ADD X12, X3, X4       Instruction instruction fetch       Instruction instruction access       Write-back       Data access       Write-back         ADD X14, X5, X6       Instruction instruction fetch       Instruction instruction access       Data access       Write-back |  |  |

## Single-Cycle Pipeline Diagram

• State of pipeline in a given cycle.

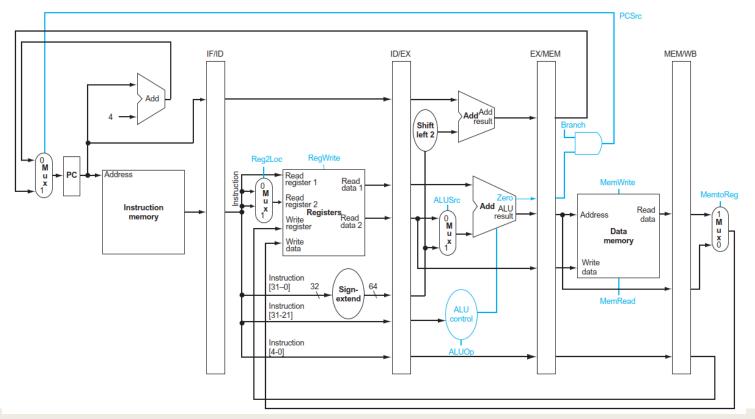

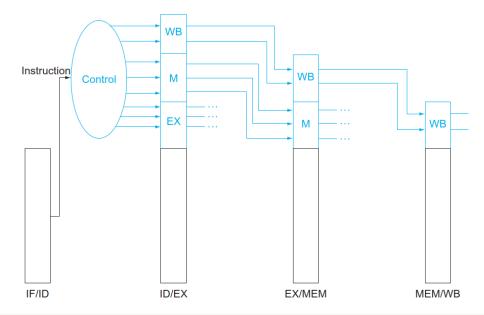

# **Pipelined Control (Simplified)**

## **Pipelined Control**

- Control signals derived from instruction

- As in single-cycle implementation

## **Pipelined Control**

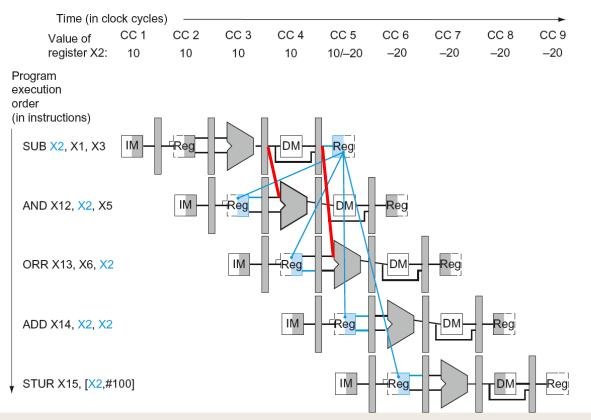

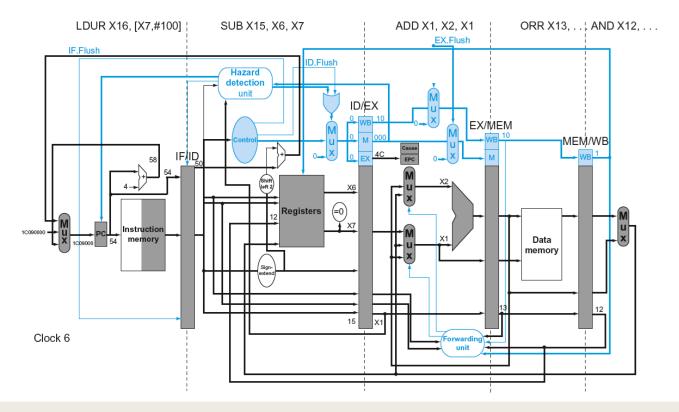

### **Data Hazards in ALU Instructions**

• Consider this sequence:

SUBX2, X1,X3// Register X2 written by SUBANDX12,X2,X5// 1st operand(X2) depends on SUBORX13,X6,X2// 2nd operand(X2) depends on SUBADDX14,X2,X2// 1st(X2) & 2nd(X2) depend on SUBSTURX15,[X2,#100]// Base (X2) depends on SUB

- We can resolve hazards with forwarding

- How do we detect when to forward?

## **Dependencies & Forwarding**

#### **Detecting the Need to Forward**

- Pass register numbers along pipeline

- e.g., ID/EX.RegisterRs = register number for Rs sitting in ID/EX pipeline register

- ALU operand register numbers in EX stage are given by

- ID/EX.RegisterRn1, ID/EX.RegisterRm2

- Data hazards when

1a. EX/MEM.RegisterRd = ID/EX.RegisterRn11b. EX/MEM.RegisterRd = ID/EX.RegisterRm2

2a. MEM/WB.RegisterRd = ID/EX.RegisterRn12b. MEM/WB.RegisterRd = ID/EX.RegisterRm2

Fwd from MEM/WB pipeline reg

- But only if forwarding instruction will write to a register!

- EX/MEM.RegWrite, MEM/WB.RegWrite

- And only if Rd for that instruction is not XZR

- EX/MEM.RegisterRd ≠ 31, MEM/WB.RegisterRd ≠ 31

## **Forwarding Paths**

# **Forwarding Conditions**

| Mux control     | Source | Explanation                                                                    |  |  |

|-----------------|--------|--------------------------------------------------------------------------------|--|--|

| ForwardA = $00$ | ID/EX  | The first ALU operand comes from the register file.                            |  |  |

| ForwardA = 10   | EX/MEM | The first ALU operand is forwarded from the prior ALU result.                  |  |  |

| ForwardA = 01   | MEM/WB | The first ALU operand is forwarded from data memory or an earlier ALU result.  |  |  |

| ForwardB = $00$ | ID/EX  | The second ALU operand comes from the register file.                           |  |  |

| ForwardB = 10   | EX/MEM | The second ALU operand is forwarded from the prior ALU result.                 |  |  |

| ForwardB = 01   | MEM/WB | The second ALU operand is forwarded from data memory or an earlier ALU result. |  |  |

## **Detection Conditions**

#### 1. EX hazard:

```

if (EX/MEM.RegWrite

and (EX/MEM.RegisterRd ≠ 31)

and (EX/MEM.RegisterRd = ID/EX.RegisterRn1)) ForwardA = 10

if (EX/MEM.RegWrite

and (EX/MEM.RegisterRd ≠ 31)

and (EX/MEM.RegisterRd = ID/EX.RegisterRm2)) ForwardB = 10

```

#### 2. *MEM hazard*:

```

if (MEM/WB.RegWrite

and (MEM/WB.RegisterRd ≠ 31)

and (MEM/WB.RegisterRd = ID/EX.RegisterRn1)) ForwardA = 01

if (MEM/WB.RegWrite

and (MEM/WB.RegisterRd ≠ 31)

and (MEM/WB.RegisterRd = ID/EX.RegisterRm2)) ForwardB = 01

```

## **Double Data Hazard**

• Consider the sequence:

add X1,X1,X2 add X1,X1,X3 add X1,X1,X4

- Both hazards occur

- We want to use the most recent data

- Revise MEM hazard condition

- Only fwd if EX hazard condition isn't true

## **Double Data Hazard**

• MEM hazard revised:

```

if (MEM/WB.RegWrite

and (MEM/WB.RegisterRd ≠ 31)

and not(EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 31)

and (EX/MEM.RegisterRd ≠ ID/EX.RegisterRn1))

and (MEM/WB.RegisterRd = ID/EX.RegisterRn1)) ForwardA = 01

if (MEM/WB.RegWrite

and (MEM/WB.RegisterRd ≠ 31)

and not(EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 31)

and (EX/MEM.RegisterRd ≠ ID/EX.RegisterRm2))

and (EX/MEM.RegisterRd = ID/EX.RegisterRm2)) ForwardB = 01

```

## **Datapath with Forwarding**

### **Load-Use Hazard Detection**

- One case where forwarding cannot save the day is when an instruction tries to read a register following a load instruction that writes the same register.

- In that case it is necessary to **stall** the pipeline.

- We check this condition when the using instruction is decoded in ID stage

- The ALU operand register numbers in ID stage are given by

- IF/ID.RegisterRn1, IF/ID.RegisterRm2

- We have a Load-Use hazard when

- ID/EX.MemRead and ((ID/EX.RegisterRd = IF/ID.RegisterRn1) or (ID/EX.RegisterRd = IF/ID.RegisterRm2))

- If detected, we must stall and insert bubble.

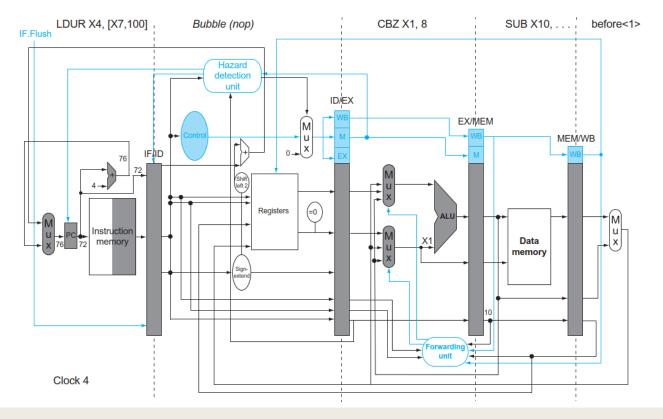

## How to Stall the Pipeline

- Force control values in ID/EX register to 0

- EX, MEM and WB do nop (no-operation)

- Prevent update of PC and IF/ID register

- The decoded instruction is decoded again

- The following instruction is fetched again

- 1-cycle stall allows MEM to read data for LDUR

- Can subsequently forward to EX stage

#### Load-Use Hazard

#### **Datapath with Hazard Detection**

## **Stalls and Performance**

- Although the compiler generally relies upon the hardware to resolve hazards and thereby ensure correct execution, the compiler must understand the pipeline to achieve the best performance.

- Otherwise, unexpected stalls will reduce the performance of the compiled code.

- Stalls reduce performance

- But are required to get correct results

- Compiler can arrange code to avoid hazards and stalls

- Requires knowledge of the pipeline structure

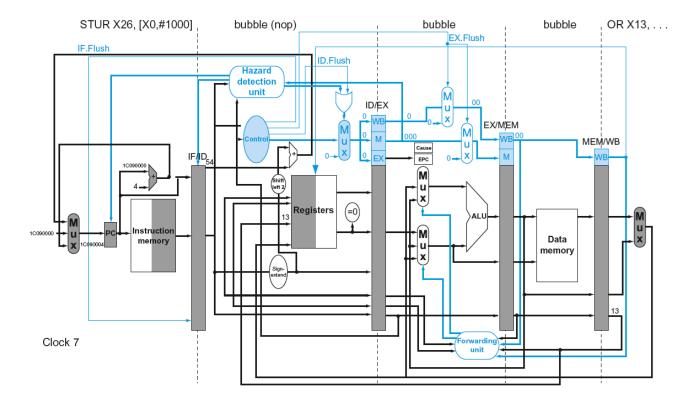

## **Branch Hazards**

#### • If branch outcome determined in MEM

UNIVERSITÀ DEGLI STUDI DI TRIESTE

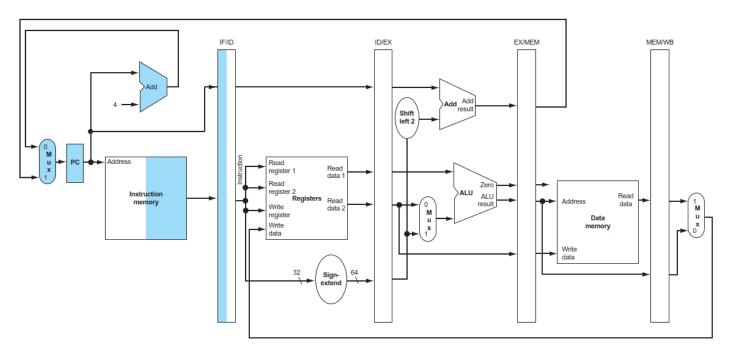

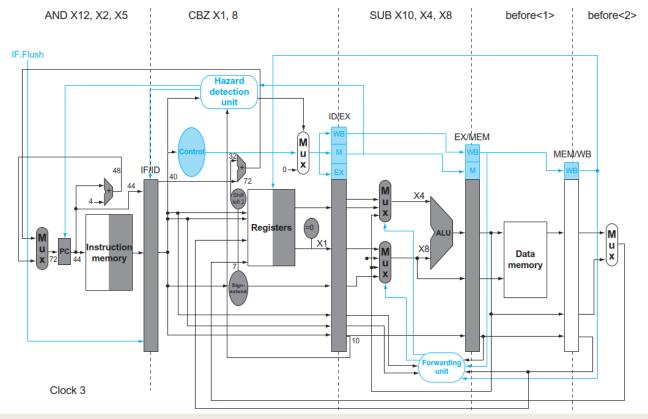

## **Reducing Branch Delay**

- If we move the conditional branch execution earlier in the pipeline, then fewer instructions need be flushed.

- Moving the branch decision up requires two actions to occur earlier:

- computing the branch target address and

- evaluating the branch decision.

- Moving the branch test to the ID stage implies **additional forwarding** and **hazard detection** hardware.

- During ID, we must decode the instruction, decide whether a bypass to the zero test unit is needed, and complete the zero test so that if the instruction is a branch, we can set the PC to the branch target address. The bypassed source operands of a branch can come from either the ALU/MEM or MEM/WB pipeline latches.

- Because the value in a branch comparison is needed during ID but may be produced later in time, it is possible that a data hazard can occur and a stall will be needed.

- If an **ALU** instruction immediately preceding a branch produces the operand for the test in the conditional branch, **a stall** will be required.

- If a **load** is immediately followed by a conditional branch that depends on the load result, **two stall** cycles will be needed.

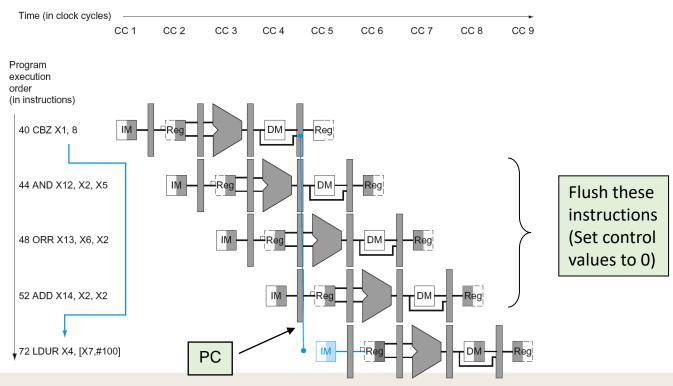

# **Example: branch taken**

| 36: | SUB  | X10, | X4,  | X8   |

|-----|------|------|------|------|

| 40: | CBZ  | X1,  | ΧЗ,  | 8    |

| 44: | AND  | X12, | X2,  | X5   |