# Developing on Xilinx Zynq using C to RTL automatic conversion

Accelerating Your Success"

# **Objectives**

- Introduce Avnet Silica

- Understand the Zynq-7000 All Programmable SoC architecture

- Introduce the Vivado High Level Synthesis

- Automatic conversion from C/C++ to VHDL/Verilog

- Introduce Avnet Silica

- Understand the Zynq-7000 All Programmable SoC architecture

- Introduce the Vivado High Level Synthesis

Automatic conversion from C/C++ to VHDL/Verilog

# **Objectives**

- Introduce Avnet Silica

- Understand the Zynq-7000 All Programmable SoC architecture

- Introduce the Vivado High Level Synthesis

Automatic conversion from C/C++ to VHDL/Verilog

# System Bottlenecked?

#### • Profiling indicates processor activity

- Is processor utilization exceeding 90%?

- o Processor Queue Length > 2?

- If multiprocessor system, processor time > 50%?

- o Intensive reoccurring tasks?

- Effects of overburdened Processors include:

- Increased Data Latency

- Delayed Interrupt Handling

- Lowered Data Throughput

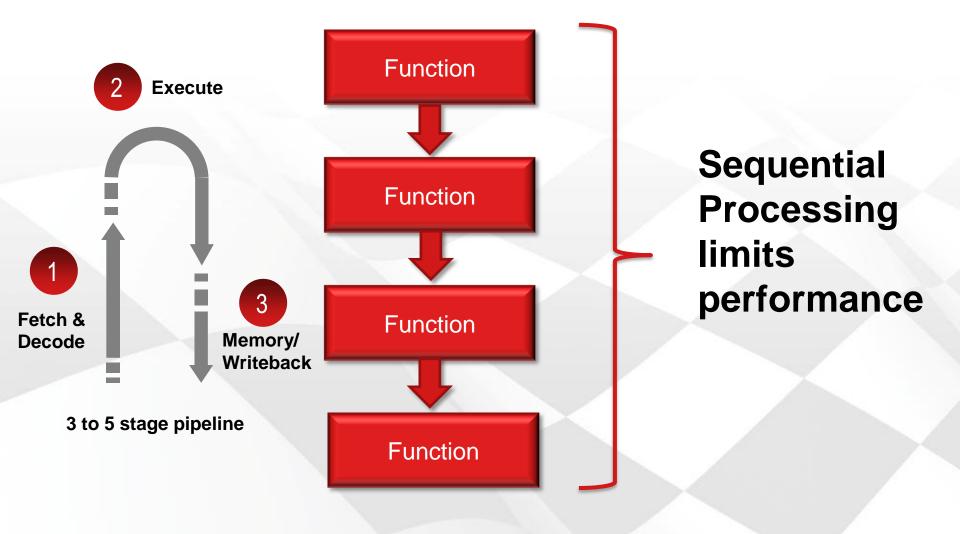

# Software Engineers: Stuck in a Sequential World

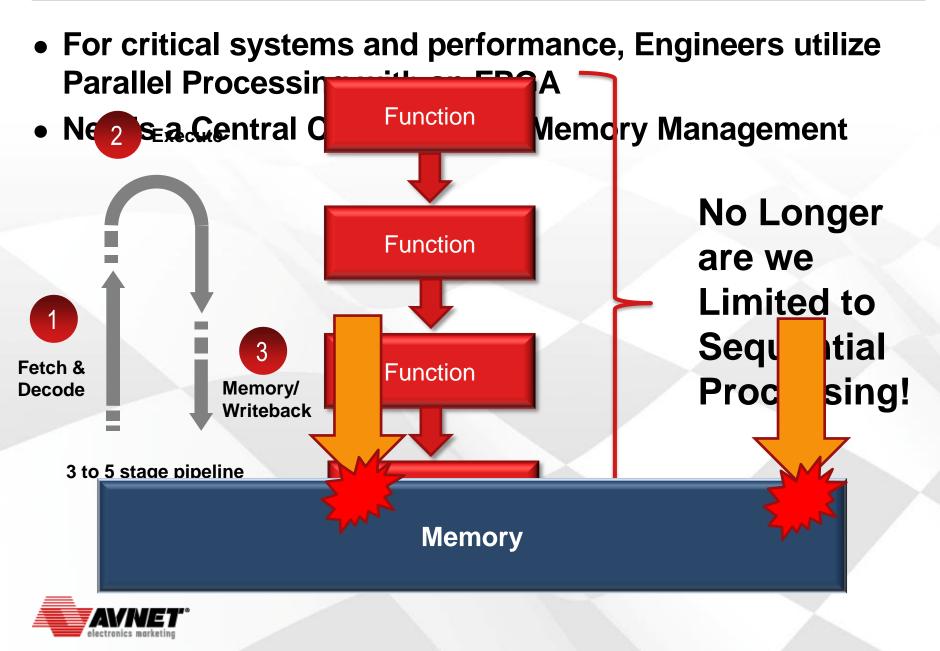

# Parallel Processing is Efficient...

#### The First All Programmable SoC

AMB

ARM

AZ MALAN MIZAN AZ M

ELECTRON D'OR

#### Significant Customer Adoption and Momentum

- ✓ In full production since March 2013, ES since 2012

- ✓ 500+ unique customers actively designing

- 100+ Zynq specific partners

- All major OSs supported and in use

- ✓ 20+ different development boards and SOMs

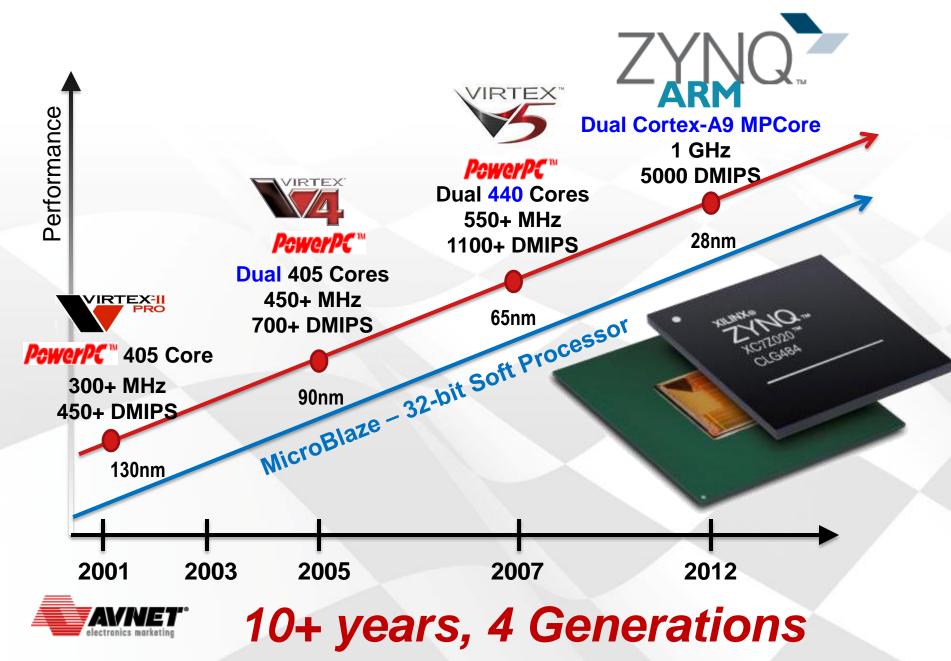

# **Xilinx Processing Heritage**

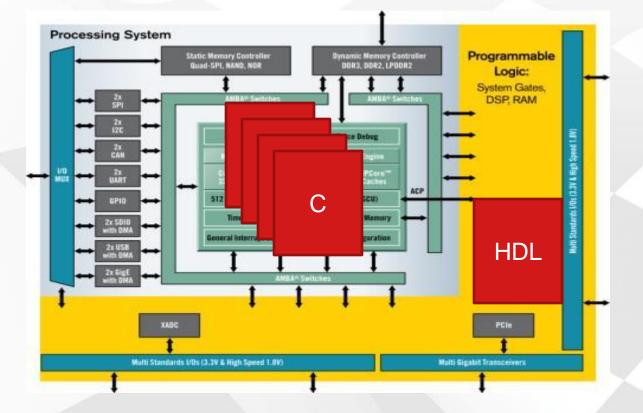

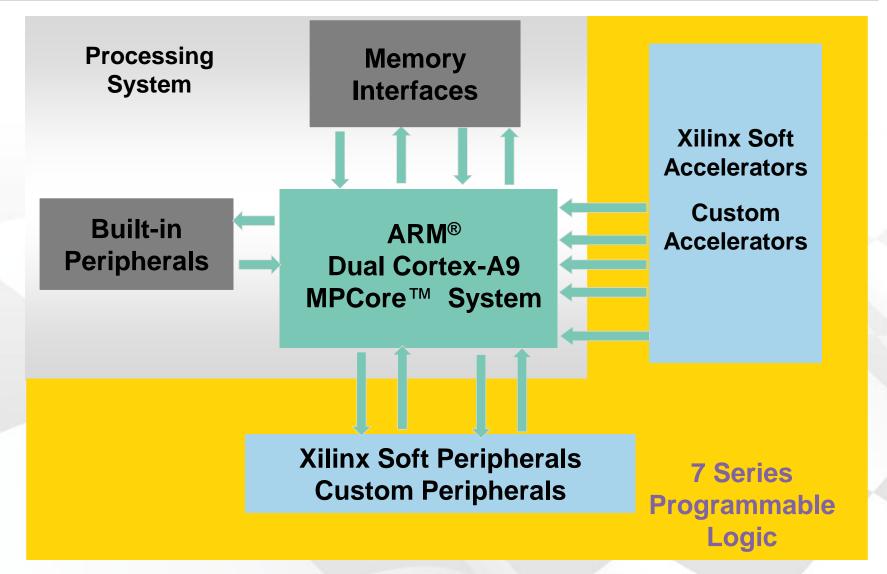

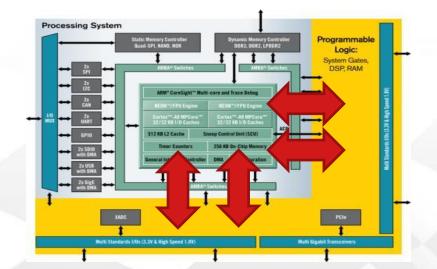

# Zynq-7000 AP SoC Basic Architecture

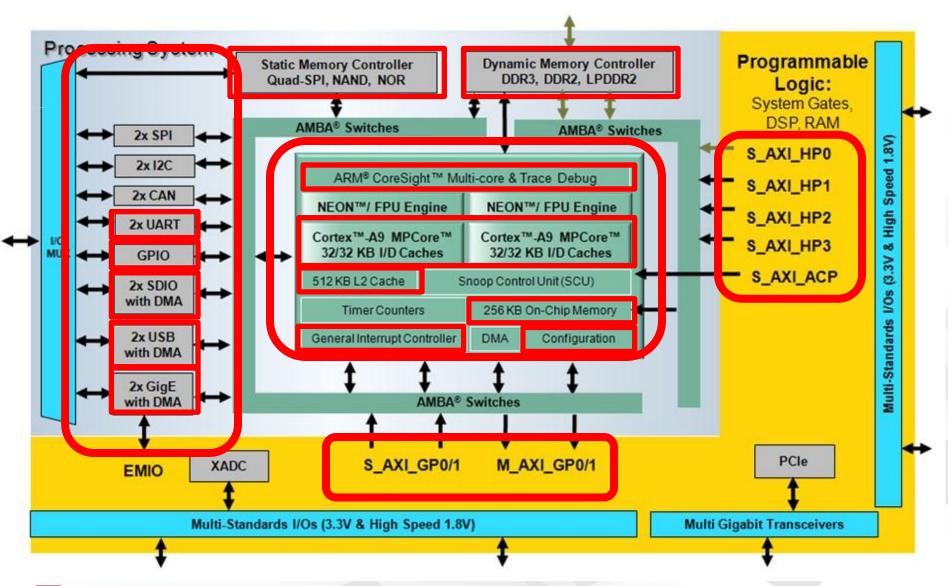

# Zynq-7000 AP SoC Block Diagram

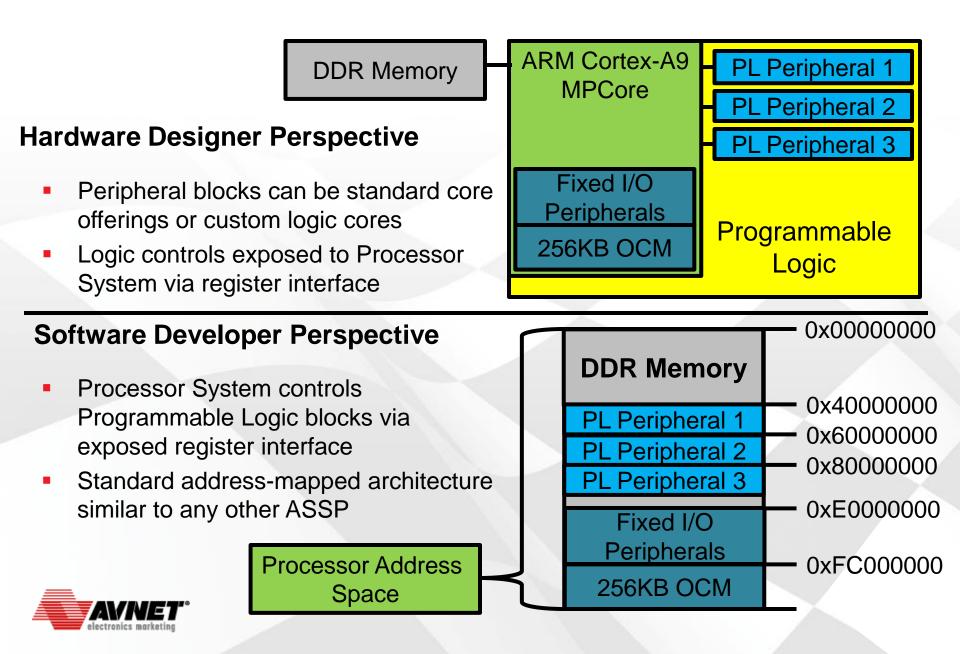

# Connecting HW and SW

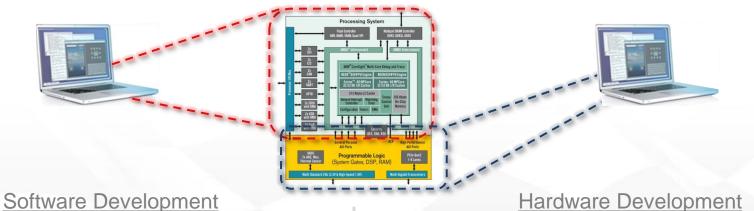

#### Parallel Developments of your AP SoC Based Application

Processor boots first like any ARM based SoC.

- SW developers can use their favorite SW tool to load / debug SW code over JTAG

- Programmable Logic can be left unconfigured while developing on real hardware

Reference SW boots processor first leaving PL up and ready to be programmed through JTAG

- Vivado Probe connects to Programmable Logic like to any other FPGA

- FPGA developer can start loading / debug like for any FPGA

SW developments like any other ARM based SoC

HW developments like any other Xilinx FPGA

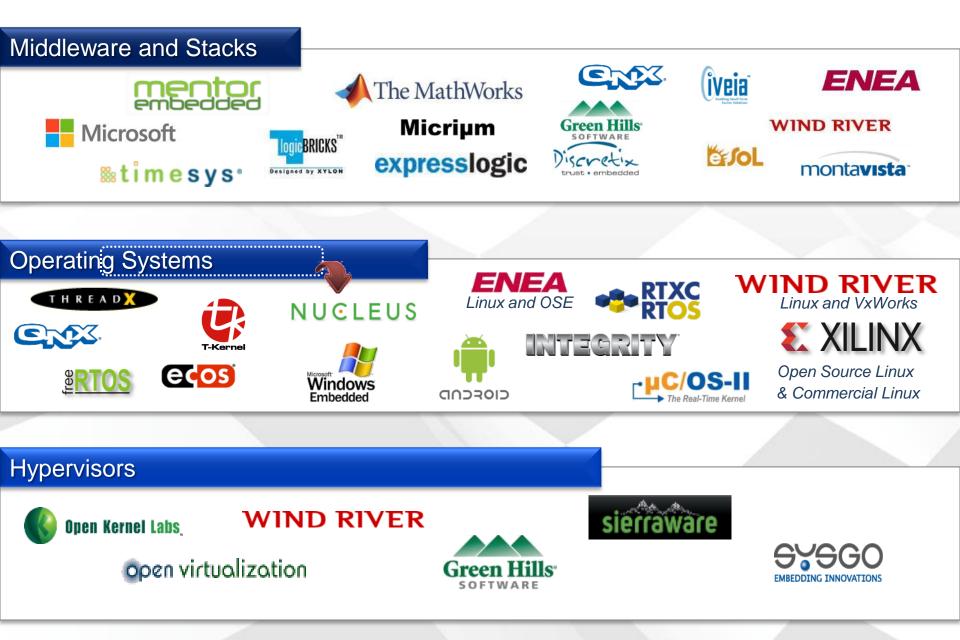

#### Extensive OS, Middleware & Stack Ecosystem

# Zynq-7000 Device Portfolio Summary

#### Scalable platform offers easy migration between devices

|                    | Zynq-7000 AP SoC<br>Devices                 | Z-7010            | Z-7015            | Z-7020                       | Z-7030                                                        | Z-7045             | Z-7100            |  |

|--------------------|---------------------------------------------|-------------------|-------------------|------------------------------|---------------------------------------------------------------|--------------------|-------------------|--|

| Processing System  | Processor Core                              |                   |                   | Dual ARM® Cori               | ll ARM® Cortex™-A9 MPCore™                                    |                    |                   |  |

|                    | Processor Extensions                        |                   | NEON              | <sup>M</sup> & Single / Doul | le Precision Floating Point                                   |                    |                   |  |

|                    | Max Frequency                               |                   | 866 MHz           |                              | Up to 1 GHz                                                   |                    |                   |  |

|                    | Memory                                      |                   | L1 Cache 32ł      | BI/D, L2 Cach                | 512KB, on-chip Memory 256KB                                   |                    |                   |  |

|                    | External Memory Support                     |                   | DDR3, D           | DR3L, DDR2, LP               | DDR2,2x QSPI, NAND, NOR                                       |                    |                   |  |

|                    | Peripherals                                 | 2                 |                   |                              | Tri-mode Gigabit Ethernet,<br>0B, 2x I2C, 2x SPI, 4x 32b GPIO |                    |                   |  |

| Programmable Logic | Approximate ASIC Gates                      | ~430K<br>(28k LC) | ~1.1M<br>(74k LC) | ~1.3M<br>(85k LC)            | ~1.9M<br>(125k LC)                                            | ~5.2M<br>(350k LC) | ~6.6M<br>(444kLC) |  |

|                    | Block RAM                                   | 240KB             | 380KB             | 560KB                        | 1,060KB                                                       | 2,180KB            | 3,020KB           |  |

|                    | Peak DSP Performance<br>(Symmetric FIR)     | 100 GMACS         | 200GMACS          | 276 GMACS                    | 593 GMACS                                                     | 1334 GMACS         | 2662 GMACS        |  |

|                    | PCI Express®<br>(Root Complex or Endpoint)  | -                 | Gen2 x4           | -                            | Gen2 x4 Gen2 x8                                               |                    |                   |  |

| Pro                | Agile Mixed Signal (XADC)                   |                   |                   | 2x 12bit 1Ms                 | s A/D Converter                                               |                    |                   |  |

|                    | Processor System IO                         |                   |                   |                              | 30                                                            |                    |                   |  |

|                    | Multi Standards 3.3V IO                     | 100               | 150               | 200                          | 100                                                           | 212                | 250               |  |

| 2                  | Multi Standards High Performance<br>1.8V IO | -                 | -                 | -                            | 150                                                           | 150                | 150               |  |

|                    | Multi Gigabit Transceivers                  | -                 | 4                 | -                            | 4                                                             | 16                 | 16                |  |

| Â                  | AVNET                                       | 1                 |                   | 1                            |                                                               |                    |                   |  |

|                    | electronics marketing                       | MicroZec          |                   | ZedBoard                     | b                                                             |                    |                   |  |

Zynq Prototyping and Production Solutions We've got you covered!

> Over 12,000 Boards Sold!

- ZedBoard

- ZC702

- ZC706

- MicroZed

- Zynq MMP

- Zynq Mini-ITX

- IVK

- SDR

# Xilinx Embedded Tool Flow

# Vivado Design Suite WebPACK Edition FREE!

Supports <u>four</u> Zynq devices: 7010, 7015, 7020 and 7030

| Pillars of<br>Productivity        | Features                       | WebPACK | Design<br>Edition | System<br>Edition | Free 30-day<br>Eval |

|-----------------------------------|--------------------------------|---------|-------------------|-------------------|---------------------|

| IP Integration and Implementation | Integrated Design Environment  | V       | ٧                 | V                 | V                   |

|                                   | Software Development Kit (SDK) | ٧       | ٧                 | V                 | V                   |

| Verification and Debug            | Vivado Simulator               | V       | ٧                 | V                 | V                   |

|                                   | Vivado Logic Analyzer          |         | ٧                 | V                 | V                   |

|                                   | Vivado Serial Analyzer         |         | ٧                 | V                 | V                   |

| Design<br>Exploration and IP      | High-Level Synthesis           |         |                   | V                 | V                   |

| Generation                        | System Generator for DSP       |         |                   | V                 | ٧                   |

#### MicroZed and ZedBoard include license for Vivado Analyzer

# **Objectives**

- Introduce Avnet Silica

- Understand the Zynq-7000 All Programmable SoC architecture

- Introduce the Vivado High Level Synthesis

- Automatic conversion from C/C++ to VHDL/Verilog

# **Increased System Performance**

#### • Increasing SW Processing Performance with:

- Programmable Logic

- Massive DSP processing

- High throughput AXI

- Over 3000 PS to PL direct connections

- High performance I/Os

- Gigabit transceivers

| Elements            | Performance<br>(up to) |  |  |

|---------------------|------------------------|--|--|

| Processors (each)   | 1 GHz                  |  |  |

| PL Fabric/ DSP Fmax | 741 MHz                |  |  |

| DSP (aggregate)     | 1080 GMACs             |  |  |

| Transceivers (each) | 12.5Gbps               |  |  |

# **Increased System Performance**

### Optimized & Simplified HW/SW Partitioning

- HW acceleration enables scaling SW performance to address many applications

- Low latency interfacing for efficient co-processor implementation and high throughput data transfers