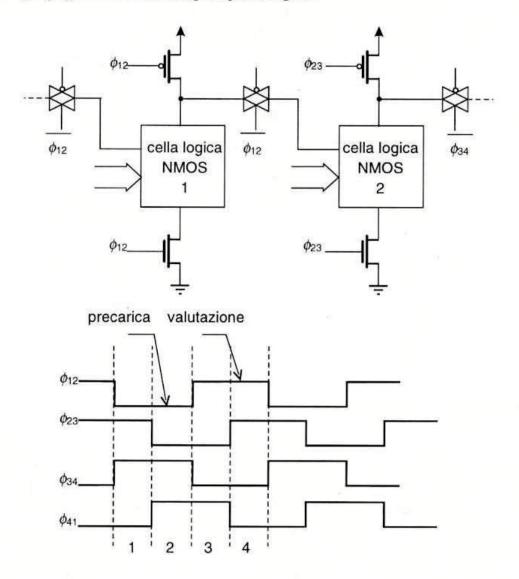

zione; anche per questa logica vale quanto detto per la logica a due fasi sul periodo minimo dei segnali di fase, che deve essere significativamente più elevato del ritardo di propagazione di una singola porta logica.

Figura 11.25 Schema di un circuito logico a quattro fasi

## 11.7 Logica dinamica Domino

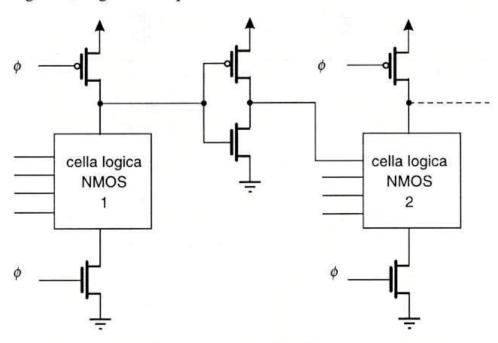

La struttura logica dinamica detta "Domino" è una delle logiche dinamiche più utilizzate nei circuiti VLSI; essa deriva dalla logica ad una fase, in quanto utilizza una sola fase per sincronizzare tutte le celle logiche del circuito, ma con una modifica fondamentale che elimina l'inconveniente dovuto alla possibile scarica della capacità di ingresso nel transitorio di valutazione della cella a monte. Lo schema della cella elementare è riportato in Figura 11.26; in questo si ritrovano i transistori PMOS di precarica e NMOS di valutazione della singola cella logica, ma lungo la linea di connessione tra le celle è inserito un invertitore CMOS.

Il ruolo di questo invertitore essenzialmente è quello di invertire la transizione possibile all'uscita della cella in fase di valutazione, in modo da evitare i problemi visti nelle celle dinamiche ad una fase; inoltre esso separa l'uscita della cella precedente dagli ingressi delle altre celle, e fornisce un'elevata corrente di carica alle capacità di ingresso, migliorando quindi il fan-out della cella.

Figura 11.26 Circuito a logica dinamica Domino

Ricordiamo che nelle celle dinamiche a una fase (ma anche nelle successive), come si è visto nel Paragrafo 11.4, durante la fase di precarica l'uscita è nello stato alto, per cui nella fase di valutazione la transizione in uscita dalla cella è un passaggio condizionato dallo stato alto a quello basso, se i segnali logici agli ingressi sono tali da creare una via di conduzione nella rete di NMOS; se questa transizione non è molto veloce la fase di valutazione della cella successiva può essere alterata perché all'inizio del transitorio quest'ultima vede segnali ancora alti, mentre questi a regime dovrebbero essere bassi, e ciò può causare la scarica della capacità in uscita della cella a valle durante il transitorio di valutazione. Nella logica Domino la presenza dell'invertitore fa sì che i livelli inviati alla cella successiva siano invertiti rispetto a quelli sopra ricordati: durante lo stato di precarica, le celle successive vedono un segnale basso, e quindi gli NMOS sono aperti; durante la valutazione, l'uscita dell'invertitore (e quindi gli ingressi delle celle successive) non può che passare dal livello basso a quello alto (nel caso ovviamente che la cella precedente presenti un'uscita bassa per effetto dei segnali agli ingressi), mentre non è mai possibile la transizione dall'alto al basso.

Questo comporta che tutte le celle in un circuito Domino possono essere pilotate dallo stesso segnale di fase  $\phi$ , in quanto finché gli ingressi non effettuano delle transizioni (da 0 a 1) le celle rimangono nello stato alto; gli eventuali transitori nelle transizioni delle uscite non comportano altro che un ritardo corrispondente nell'eventuale passaggio allo stato basso delle celle pilotate da queste uscite. In

effetti durante la fase di valutazione (comune a tutte le celle) le celle in cascata passano una dopo l'altra dallo stato alto a quello basso (condizionatamente agli ingressi) con un ritardo pari al transitorio della transizione da 0 a 1, analogamente alle tessere del gioco del domino che cadono l'una dopo l'altra, ognuna spinta dalla caduta della precedente, da cui il nome della logica.

Il vantaggio evidente della logica Domino è quello di fare uso di un solo segnale di fase, con notevole semplificazione dei circuiti di sincronizzazione e di ritardo. L'uso di un solo segnale di fase riduce ai soli tempi di transizione il ritardo delle celle, eliminando i tempi morti dovuti alla successione di più fasi dei circuiti precedenti. Inoltre la presenza dell'invertitore CMOS migliora i margini di rumore e fornisce una corrente più elevata per il pilotaggio delle capacità di ingresso delle porte a valle, permettendo quindi un più elevato fan-out.

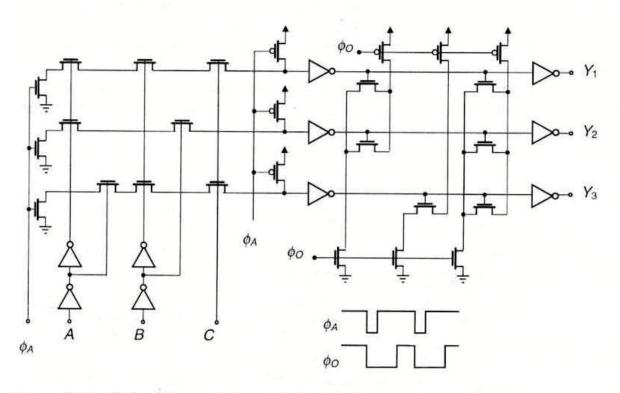

Figura 11.27 PLA a 3 ingressi, 3 termini di prodotti e tre uscite, realizzato con logica Domino

L'inconveniente di questa logica è quello di non fornire l'inversione del segnale logico all'uscita della singola cella, a causa della presenza dell'invertitore aggiuntivo; in tal modo si possono avere solo funzioni AND e OR (e le loro combinazioni), ma non funzioni NAND o NOR, il che non permette di realizzare con questo circuito qualsiasi espressione logica. L'inversione delle variabili deve essere quindi effettuata prima di entrare in una catena di celle Domino, o alla fine della stessa, ma non tra una cella e l'altra. La logica Domino è quindi particolarmente adatta a realizzare quelle funzioni logiche che non richiedono inversione in uscita: un esempio è quello delle strutture PLA viste nel Paragrafo 10.9, che richiedono i due piani AND e OR per effettuare le funzioni somma di prodotti; in questo caso

non è richiesta l'inversione in uscita dai due piani, e le due funzioni AND e OR sono direttamente implementate nelle celle Domino.

In Figura 11.27 è riportato come esempio lo schema circuitale di un PLA con 3 ingressi, 3 termini di prodotto e 3 termini di somme, realizzato con logica Domino. I segnali di fase  $\phi_A$  e  $\phi_O$  rispettivamente per il piano AND e quello OR, che in principio possono essere un unico segnale, sono di diversa durata per il valore basso (fase di precarica), in modo che la valutazione del piano AND preceda temporalmente quella del piano OR e permetta il completamento della fase di valutazione del primo anteriormente a quella del secondo.

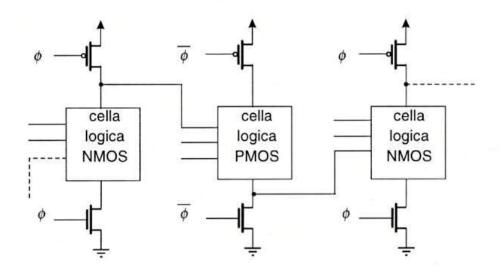

## 11.8 Logica NORA CMOS

Una struttura logica derivata dalla logica Domino e che permette l'inversione delle variabili in uscita è quella detta NORA da "no race" in quanto questa logica non ha problemi di "corsa" o transitori degli ingressi come quelli dei circuiti a una fase, pur eliminando l'invertitore presente nella logica Domino.

Il circuito utilizza alternativamente per le singole celle logiche transistori NMOS e PMOS, per cui viene chiamata anche logica "Domino NP", e il funzionamento di questa logica è schematizzato nella Figura 11.28.

Figura 11.28 Logica Domino modificata, o NORA

La prima cella contiene una rete NMOS e quindi in fase di precarica la sua uscita è alta. La cella successiva è realizzata con transistori PMOS ed il segnale di fase è invertito rispetto a quello della cella precedente, per cui nella fase di precarica il NMOS conduce e il PMOS è aperto; in effetti per la cella P la fase di precarica è svolta dal NMOS e quella di valutazione dal PMOS. L'uscita della seconda cella in precarica è quindi bassa, e durante la fase di valutazione può portarsi condizionatamente alta se tutti gli ingressi (della rete PMOS) sono bassi. Il funzionamento è analogo a quello della logica Domino, con la variante che le celle sono alternativa-

mente a precarica bassa e alta, e al posto dell'inversione dell'uscita vengono utilizzati MOS alternativamente P e N che di fatto invertono le variabili di ingresso.

Anche in questa logica le singole uscite effettuano al più un'unica transizione che porta sempre i MOS della cella successiva ad andare dall'interdizione alla conduzione, eliminando così i problemi della scarica delle capacità della cella a valle durante i transitori. Il vantaggio di questa logica è quello di permettere espressioni logiche con inversione delle variabili in uscita e quindi di realizzare qualunque funzione logica, al contrario della logica Domino. L'inconveniente è quello di usare per le celle P reti di transistori PMOS, che sono, come si è visto, intrinsecamente più lenti a parità di area occupata. Inoltre, non essendovi lo stadio invertitore, i margini di rumore sono più bassi.

## 11.9 Confronto tra le logiche dinamiche

I circuiti logici dinamici hanno un significativo campo di applicazione nei circuiti integrati ad alta densità di integrazione, in quanto come si è visto richiedono un minor numero di transistori elementari rispetto alle versioni a logica pienamente complementare FCMOS.

Vi sono anche altri aspetti che differenziano le prestazione di queste logiche da quelle statiche. In particolare, per quanto riguarda i margini di rumore, le logiche dinamiche hanno un valore  $V_{IL}$  minore di quello delle porte FCMOS, in quanto la capacità di uscita della cella comincia a scaricarsi quando gli ingressi superano il valore  $V_T$  di soglia dei MOS, mentre per le porte FCMOS  $V_{IL} \cong V_{DD}/2$ . La riduzione del valore di soglia logica d'altra parte comporta una riduzione dei tempi di propagazione della cella dinamica, in quanto la porta inizia a commutare quando gli ingressi raggiungono il valore  $V_T$  e quindi prima dell'istante in cui raggiungono  $V_{DD}/2$ .

Per quanto riguarda l'occupazione di area, le logiche statiche FCMOS a *m* ingressi richiedono 2*m* transistori, mentre quelle dinamiche richiedono *m* transistori per la cella logica, più 2 transistori di precarica e di valutazione, più eventualmente altri 2 transistori per la porta di trasmissione o per l'invertitore.

Infine, per quanto riguarda i tempi di propagazione, occorre considerare diversamente le due transizioni nelle differenti logiche. Il passaggio da 0 a 1 dell'uscita per le celle dinamiche (e per le celle N della logica NORA) è effettuato durante la fase di precarica e quindi non è legato all'arrivo dei segnali in ingresso, per cui non è possibile valutare il tempo di propagazione  $t_{PLH}$ . Per le logiche pseudo-NMOS, la riduzione della capacità di uscita (corrispondente all'ingresso della cella successiva) rispetto alla logica FCMOS è bilanciato dalla riduzione della corrente di carica perché parte di questa viene assorbita dalla rete NMOS. Per quanto riguarda il passaggio da 1 a 0, nelle logiche dinamiche a 2 o 4 fasi la capacità di uscita è equivalente a quella del caso pseudo-NMOS ma la scarica della capacità dipende anche dal numero dei MOS connessi in serie nella via verso la massa, numero che è maggiorato (rispetto alla logica FCMOS e pseudo-NMOS) dal NMOS di valutazione e da quello della