### Introduzione alle FPGA

Lab 2

Prof. Laura Gonella

Laboratorio di Acquisizione e Controllo Dati a.a. 2024-25

# Examples and exercises

- Example: OR gate

- Exercise 1: AND gate

- Exercise 2: 2to1 MUX

- Example: OR gate with "process"

- Example: D-FF

- Exercise 3: 2to1 MUX with "process" and "if" statement

- Exercise 4: D-FF with synchronous reset

- Exercise 5: Shift register

### process statement

- The process statement is used in VHDL to define blocks to be evaluated sequentially

- Statements inside a process are evaluated sequentially (like most programming languages)

- Multiple process blocks are evaluated concurrently

- A process can have a sensitivity list

- List of signal to which the process is sensitive (for example a clock)

- The process is executed only when there is a change to a signal in the sensitivity list

- Processes are used to define a block of combinational logic or a block of sequential logic the latter is far more used

## Example: OR gate with process statement

```

design.vhd

1 -- Simple OR gate design

2 library IEEE;

3 use IEEE.std_logic_1164.all;

5 entity or_gate is

6 port(

a: in std_logic;

b: in std_logic;

9 q: out std_logic);

10 end or_gate;

12 architecture rtl of or_gate is

signal or_g1 : std_logic;

14 begin

15 or_g1 <= a or b;

16 q <= or_g1;</pre>

17 end rtl;

```

#### Could have been written as:

```

architecture rtl of or_gate is

begin

q <= a or b;

end rtl</pre>

```

```

design.vhd

1 -- Simple OR gate design

2 library IEEE;

3 use IEEE.std_logic_1164.all;

5 entity or_gate is

port(

a: in std_logic;

b: in std_logic;

a: out std_logic);

10 end or_gate;

12 architecture rtl of or_gate is

13 begin

process(a, b) is

begin

q \ll a \text{ or } b;

end process:

18 end rtl;

```

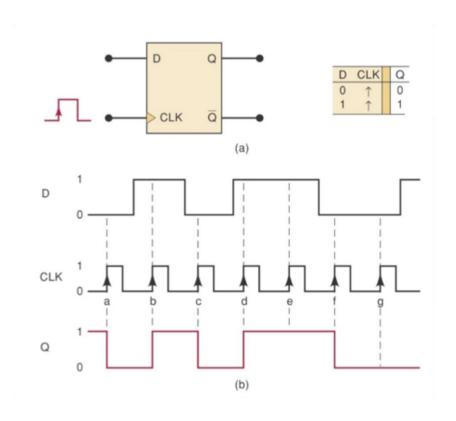

## Example of sequential logic with process: D-FF design

```

-- Code your design here

library IEEE;

use IEEE.std_logic_1164.all;

entity DFF is

port(

: in

std_logic;

CLK :in

std_logic;

: out std_logic);

end DFF;

architecture rtl of DFF is

begin

16

process (CLK)

17

18

begin

if rising_edge(CLK) then

19

Q \ll D;

20

end if:

end process;

end rtl;

```

## Edge detection

```

-- Code your design here

library IEEE;

use IEEE.std_logic_1164.all;

entity DFF is

port(

: in std_logic;

CLK :in

std_logic;

: out std_logic);

end DFF;

13 architecture rtl of DFF is

begin

process (CLK)

begin

if rising_edge(CLK) then

0 <= D;

21 end p

22 end p

23

24 end rtl;

25

26

end if:

end process:

```

### process block

- In this example, the sensitivity list contains the clock signal, CLK

- The process is executed only when there is a change to the clock

### rising\_edge(CLK)

- functions to detect signal and clock edges in the ieee.std\_logic\_1164.all package

- rising\_edge(s) returns true, if there is a rising edge on the signal s

- falling\_edge(s) returns true, if there is a falling edge on the signal s

### Conditional statement: if

```

-- Code your design here

library IEEE;

use IEEE.std_logic_1164.all;

entity DFF is

port(

: in std_logic;

std_logic;

CLK :in

: out std_logic);

end DFF;

13 architecture rtl of DFF is

begin

process (CLK)

begin

if rising_edge(CLK) then

20

21

22

end p

23

24 end rtl;

25

26

Q \ll D;

end if:

end process:

```

- Conditional statement: if

- Conditional execution inside a process

- Condition should return a Boolean (true/false)

- Keywords: if, elsif, and else

```

if <condition1 > then

<vhdl statement >;

end if;

```

```

if <condition1 > then

<vhdl statement 1 >;

else

<vhdl statement 2 >;

end if;

```

```

if <condition1> then

<vhdl statement 1>;

elsif <condition2> then

<vhdl statement 2>;

else

<vhdl statement 3>;

end if;

```

### Conditional statement: if

```

-- Code your design here

library IEEE;

use IEEE.std_logic_1164.all;

entity DFF is

port(

: in std_logic;

CLK :in

std_logic;

: out std_logic);

end DFF;

13 architecture rtl of DFF is

begin

process (CLK)

begin

if rising_edge(CLK) then

20 (

21 end p

22 end p

23 24 end rtl;

25 26

Q \ll D;

end if;

end process;

```

#### Conditional statement: if

|                          | perators: |                                                                               |  |

|--------------------------|-----------|-------------------------------------------------------------------------------|--|

| =                        | equal     | equal                                                                         |  |

| /=                       | not e     | not equal                                                                     |  |

| <                        | less tl   | less than                                                                     |  |

| <=                       | less tl   | less than or equal                                                            |  |

| >                        | greate    | greater than                                                                  |  |

| >= greater than or equal |           | er than or equal                                                              |  |

| ogical ope               |           |                                                                               |  |

| not a                    |           | true if <i>a</i> is false                                                     |  |

| not a                    |           | true if <i>a</i> is false true if <i>a</i> and <i>b</i> are true              |  |

|                          |           |                                                                               |  |

| a and b                  |           | true if <i>a</i> and <i>b</i> are true                                        |  |

| a and b                  |           | true if <i>a</i> and <i>b</i> are true  true if <i>a</i> or <i>b</i> are true |  |

| a and b a or b a nand b  |           | true if a and b are true  true if a or b are true  true if a or b is false    |  |

# Example of sequential logic with process: D-FF testbench

5 library IEEE;

6 use IEEE.std\_logic\_1164.all; Library 8 entity TB\_DFF is 9 -- empty 10 end TB\_DFF; 12 architecture behavioral of TB\_DFF is 14 -- Component declaration of the D Flip-Flop • Entity (empty) component DFF is : in std\_logic; CLK :in std\_logic; : out std\_logic); -- Signals to connect to the D flip-flop signal D : STD\_LOGIC := '0'; Architecture signal CLK : STD\_LOGIC := '0'; signal Q : STD\_LOGIC; Declaritive part signal StopClock : BOOLEAN; -- boolean number (true or false) constant Period : TIME := 10 ns: -- constant 30 begin Component declaration - Instantiate the D flip-flop DUT: DFF port map(D, CLK, Q); Signal declaration -- Clock generation process ClockGenerator: process while not StopClock loop Clk <= '0'; wait for Period/2; Clk <= '1';</pre> Implementation part wait for Period/2; end loop; wait; end process ClockGenerator; Component instantiation -- Stimulus process stim\_proc: process Clock generation process begin d <= '0'; wait for 20 ns; Stimulus process d <= '1'; 55 wait for 20 ns; d <= '0'; wait for 20 ns; 59 d <= '1'; 60 wait for 20 ns; 61 StopClock <= True; 63 wait; end process stim\_proc;

69 end behavioral;

### Constants in VHDL

```

architecture behavioral of TB_DFF is

-- Component declaration of the D Flip-Flop

component DFF is

port(

D : in std_logic;

CLK :in std_logic;

Q : out std_logic);

end component;

-- Signals to connect to the D flip-flop

signal D : STD_LOGIC := '0';

signal CLK : STD_LOGIC := '0';

signal Q : STD_LOGIC;

signal StopClock : BOOLEAN; -- boolean number (true or false)

constant Period : TIME := 10 ns; -- constant

begin

```

### <u>Architecture – Declaritive part</u>

- Component declaration

- Signals declaration

- Note the signals and constant to be used for the clock generation process

#### constant

- Can be defined in process, architecture or package blocks

- := assignment operator for constants

### Clock simulation

Signals and constant for clock generation process defined in the declaritive part of the architecture

```

signal CLK : STD_LOGIC := '0';

signal StopClock : BOOLEAN; -- boolean number (true or false)

27

constant Period : TIME := 10 ns; -- constant

begin

-- Instantiate the D flip-flop

DUT: DFF port map(D, CLK, Q);

33

-- Clock generation process

ClockGenerator: process

begin

while not StopClock loop

Clk <= '0';

wait for Period/2;

Clk <= '1';

wait for Period/2;

47 -- Stimulus process

stim_proc: process

end loop;

wait:

d <= '0';

wait for 20 ns:

end process ClockGenerator;

d <= '1';

wait for 20 ns;

57

wait for 20 ns;

wait for 20 ns;

StopClock <= True;</pre>

wait;

end process stim_proc;

69 end behavioral;

```

#### <u>Architecture – Implemenation part</u>

- Component instantiation

- Clock generation process

- Simple to define in testbenches

- Can be running indefinitely or for a finite number of clock cycles

- In this example, we use the signal StopClock to stop the clock

### Clock simulation

27

28

signal CLK : STD\_LOGIC := '0';

Signals and constant for clock generation process defined in the declaritive part of the architecture

constant Period : TIME := 10 ns; -- constant

signal StopClock : BOOLEAN; -- boolean number (true or false)

```

begin

-- Instantiate the D flip-flop

DUT: DFF port map(D, CLK, Q);

33

34

Clock generation process

ClockGenerator: process

begin

while not StopClock loop

Clk <= '0':

wait for Period/2;

Clk <= '1';

wait for Period/2;

47 -- Stimulus process

stim_proc: process

end loop;

wait:

d <= '0';

wait for 20 ns;</pre>

end process ClockGenerator;

d <= '1';

wait for 20 ns;

57

wait for 20 ns;

d <= '1';

wait for 20 ns;

StopClock <= True;</pre>

wait;

end process stim_proc;

69 end behavioral;

```

### <u>Architecture – Implemenation part</u>

- Component instantiation

- Clock generation process

- Examples of clock generation syntax

```

architecture behavior of testbench is

signal clk : std_logic := '0';

begin

clk <= not clk after 5 ns;

end behavior;</pre>

```

```

architecture behavior of testbench is

signal clk : std_logic := '0';

constant CLK_PERIOD : time := 10 ns;

begin

clk <= not clk after CLK_PERIOD/2;

end behavior;</pre>

```

```

architecture behavior of testbench is

signal clk : std_logic := '0';

constant NCYCLES : integer := 100;

begin

clk_proc : process

begin

for I in 0 to NCYCLES-1 loop

clk <= not clk;

wait for 5 ns;

clk <= not clk;

wait for 5 ns;

end loop;

wait;

end process;

end behavior;</pre>

```

#### while and for statements

#### while statement

- Repeats a block of code as long as the condition is true.

- The condition is evaluated before each iteration.

- Used for loops where the number of iterations is not known beforehand.

#### for statement

- Repeats a block of code a fixed number of times.

- The loop variable automatically iterates over the specified range.

- Used when the number of iterations is known beforehand.

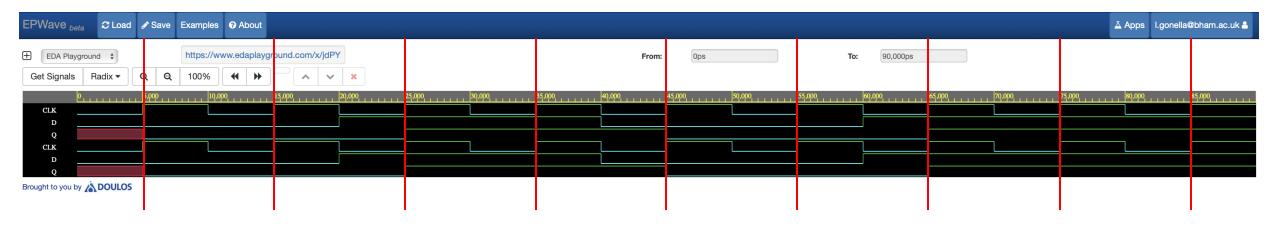

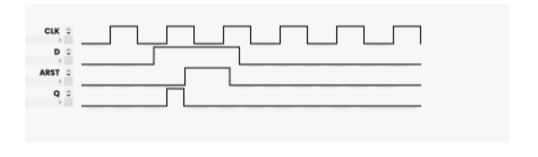

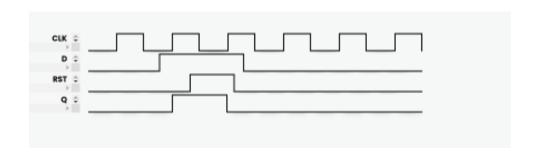

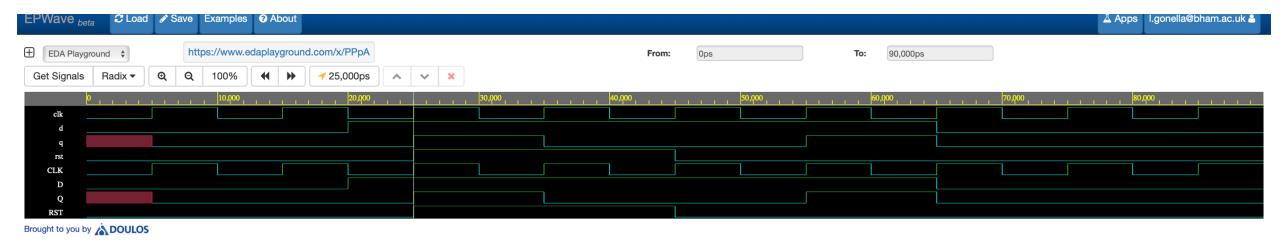

# Example of sequential logic with process: D-FF simulation waveforms

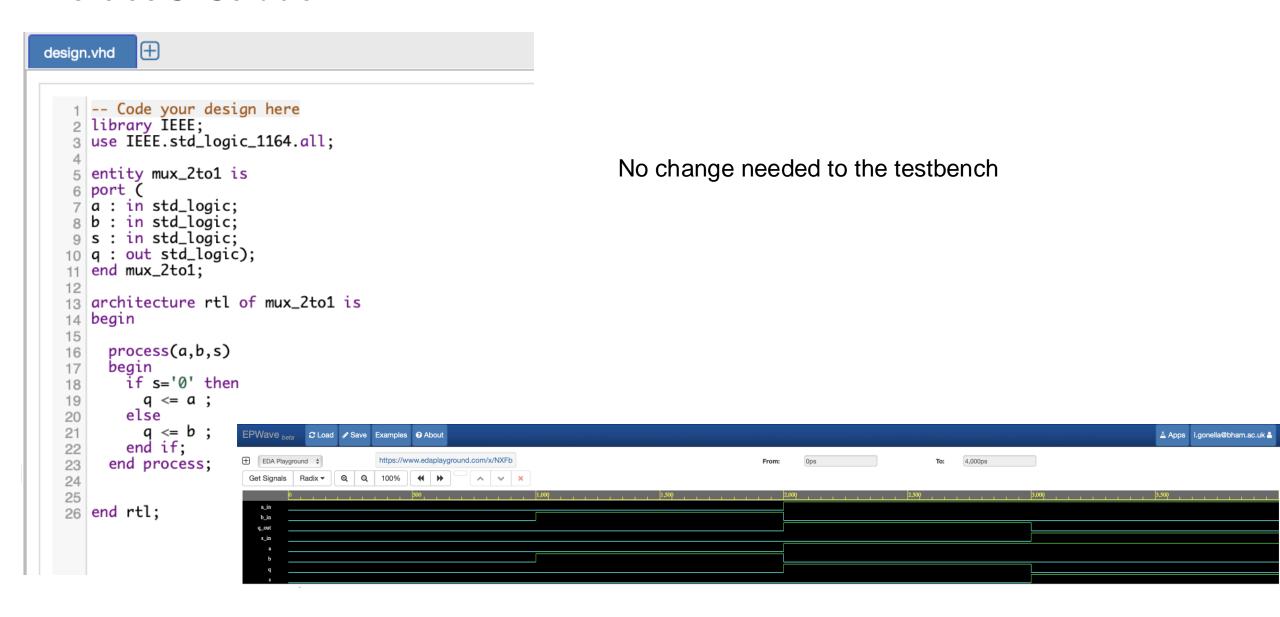

# if vs when/else

- VHDL is a concurrent language, it provides two different solutions to implement a conditional statement:

- Sequential conditional statement: if

- Concurrent conditional statement: when/else

- The sequential conditional statement can be used in process

- The concurrent conditional statement can be used in the architecture concurrent section, i.e. between the **begin/end** section of the VHDL architecture definition

- Total equivalence between if sequential statement and when/else statement; either can be used

- When using a conditional statement, one must pay attention to the final hardware implementation

- A conditional statement can be translated into a MUX or a comparator or a huge amount of combinatorial logic

### Exercise 3: MUX 2to1 code

• Rewrite the MUX example using process and the if statement

### **Exercise 3: Solution**

# End of part 2

- process statement

- Edge detection

- Conditional statement: if

- Constants in VHDL

- Clock simulation

- while and for statements

- Example: OR gate with "process"

- Example: D-FF

- Exercise 3: 2to1 MUX with "process" and "if" statement

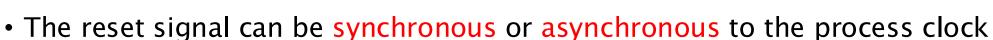

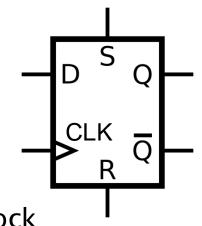

# Reset signal

process(CLK, RESET)

end if;

end process;

- Typically the D-FF have an input for the reset signal

- Upon application of the reset  $Q=0, \bar{Q}=1$

Exercise 4: Design and simulate a D-FF with synchronous reset

### **Exercise 4: Solution**

```

testbench.vhd

-- Code your testbench here

-- or browse Examples

library_IEEE;

use_IEEE.std_logic_1164.all;

entity_TB_DFF is

end TB_DFF;

architecture behavioral of TB_DFF is

-- Component declaration of the D Flip-Flop

component DFF is

port(

in std logic;

ST in std logic;

LK in std logic;

in std logic;

in std logic;

in std logic;

end component;

signal StopClock : BOOLEAN: -- boolean number (true or false)

constant Period : TIME := 10 ns; -- constant

begin

-- Instantiate the D flip-flop

DUT: DFF port map(d, rst, clk, q);

-- Clock generation process

ClockGenerator: process

ClockGenerator: process

begin

While not, $topClock loop

Clk <= 0,0

Wait for Period/2;

Wait for Period/2;

end loop;

end process ClockGenerator;

-- Stimulus process

stim_proc: process

begin

d <= '0';

wait for 20 ns;</pre>

d <= '1';

-- wait for 40 ns;

wait until rising_edge(clk);

rst <= til rising_edge(clk);

wait until rising_edge(clk);

rst <= 1.0;</pre>

wait for 20 ns;

d <= '0';

wait for 20 ns;</pre>

StopClock <= True;

wait;

end process stim_proc;

end behavioral;

```

```

design.vhd

-- Code your design here

library IEEE;

use IEEE.std_logic_1164.all;

entity DFF is

RST : in std_logic;

CLK : in std_logic;

O : out std_logic;

end DFF;

architecture rtl of DFF is

begin

process (CLK)

begin

if rising edge(CLK) then

O <= 0;

else

O <= D;

end if;

1890122345678901

end if:

end process;

end rtl;

```

### Exercise 4: Solution

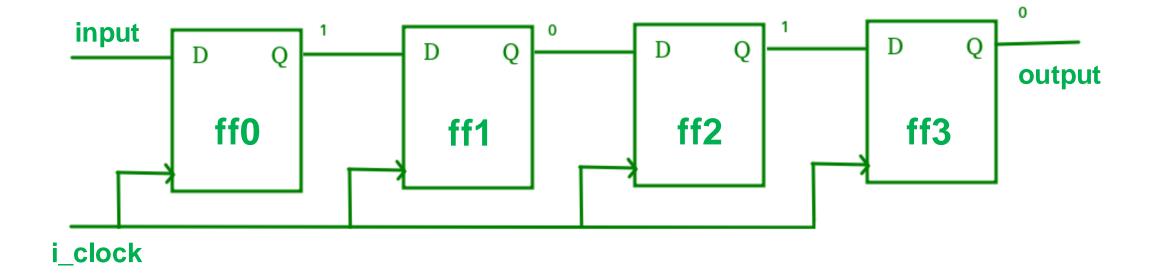

# Exercise 5: Design and simulate a shift register

• Design and simulate a shift register made of 4 D-FF with serial input, serial output

### Assigning vectors

```

signal vec : std_logic_vector(7 downto 0) := (others => '0'); -- vec is 00000000

vec <= "101000000"; -- vec is now 10100000

vec(0) <= '1'; -- vec is now 10100001

vec(2 downto 1) <= "01"; -- vec is now 10100011

vec(7 downto 5) <= vec(2 downto 0); -- vec is now 01100011</pre>

```

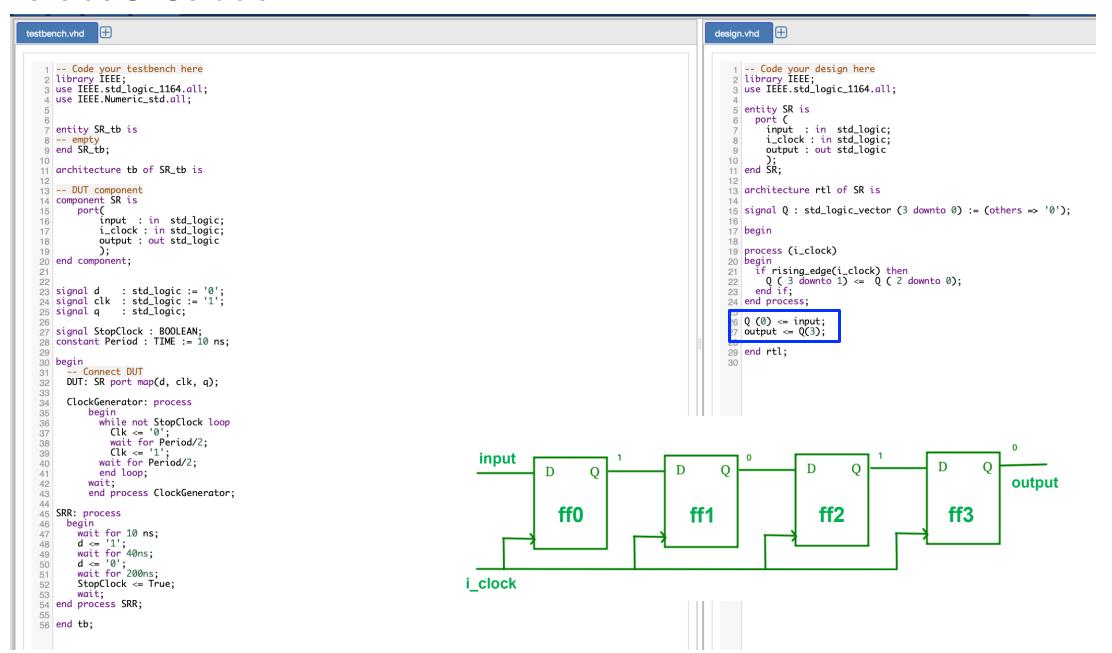

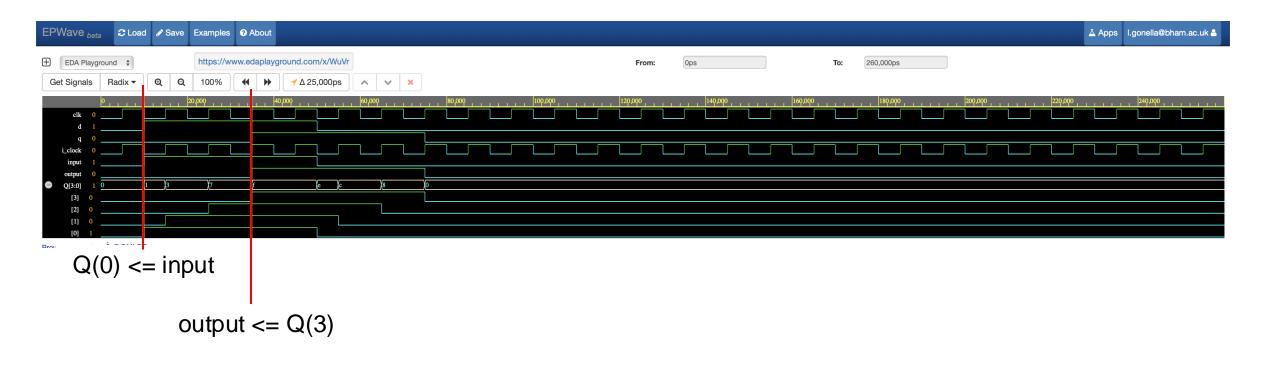

### Exercise 5: Solution A

### Exercise 5: Solution A

assignment as soon as input and Q(3) change

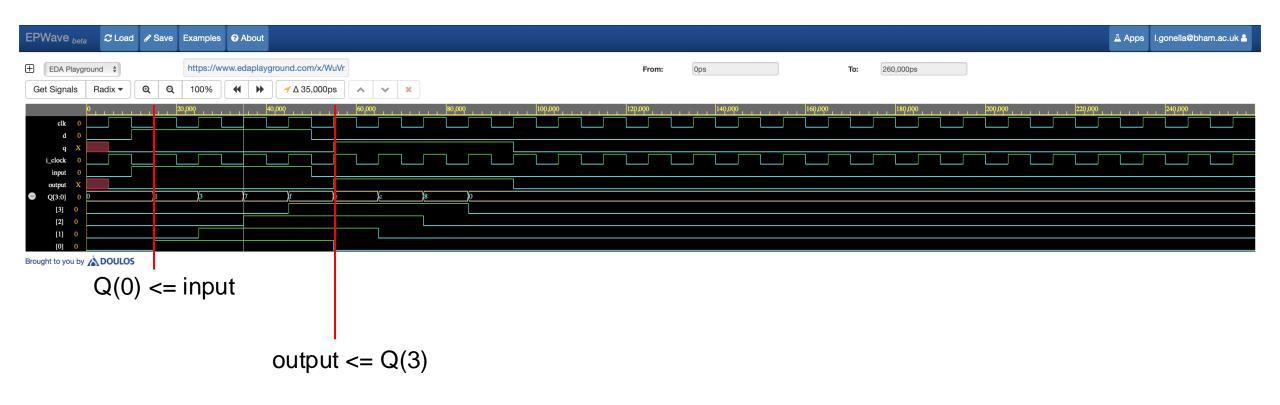

### Exercise 5: Solution B

```

testbench.vhd

design.vhd

1 -- Code your testbench here

1 -- Code your design here

2 library IEEE;

2 library IEEE;

3 use IEÉE.std_logic_1164.all;

3 use IEEE.std_logic_1164.all;

4 use IEEE.Numeric_std.all;

5 entity SR is

6 port (

7 entity SR_tb is

input : in std_logic;

8 -- empty

i_clock : in std_logic;

9 end SR_tb;

output : out std_logic

10

10

11 end SR;

11 architecture tb of SR_tb is

12

12

13 architecture rtl of SR is

13 -- DUT component

14 component SR is

15 signal Q : std_logic_vector (3 downto 0) := (others => '0');

port(

15

input : in std_logic;

16

17

i_clock : in std_logic;

17 begin

output : out std_logic

18

18

19

19 process (i_clock)

20 end component;

20 begin

21 if rising_edge(i_clock) then

21

0 (3 \text{ downto } 1) \leq 0 (2 \text{ downto } 0);

Q (0) <= input;

23 signal d : std_logic := '0';

23

output <= Q(3);

24 signal clk : std_logic := '1';

24

25 signal q : std_logic;

25

26 end process;

27 signal StopClock : BOOLEAN;

27

28 constant Period : TIME := 10 ns;

29 end rtl;

29

30 begin

31

-- Connect DUT

DUT: SR port map(d, clk, q);

32

33

34

ClockGenerator: process

35

36

while not StopClock loop

37

Clk <= '0';

wait for Period/2;

Clk <= '1';</pre>

38

39

wait for Period/2;

40

end loop;

41

42

end process ClockGenerator;

43

44

45 SRR: process

46

begin

wait for 10 ns;

47

d <= '1';

48

49

wait for 40ns;

d <= '0';

50

wait for 200ns:

51

StopClock <= True;

52

53

wait:

54 end process SRR;

55

56 end tb;

```

### Exercise 5: Solution B

assignment at the next clock rising edge

# End of part 3

- Reset signal (synch, asynch)

- Assigning vectors

- Exercise 4: D-FF with synchronous reset

- Exercise 5: Shift register

### Resources

- NANDLAND

- fpga4fun

- Free range VHLD <u>book</u>