# Circuiti in logica combinatoria

Prof.ssa Giulia Cisotto

giulia.cisotto@units.it

# MODULO 1: Architettura degli elaboratori

John Von Neumann

Matematico ed informatico di origine

ungherese che viveva e lavorava

negli Stati Uniti negli anni '40

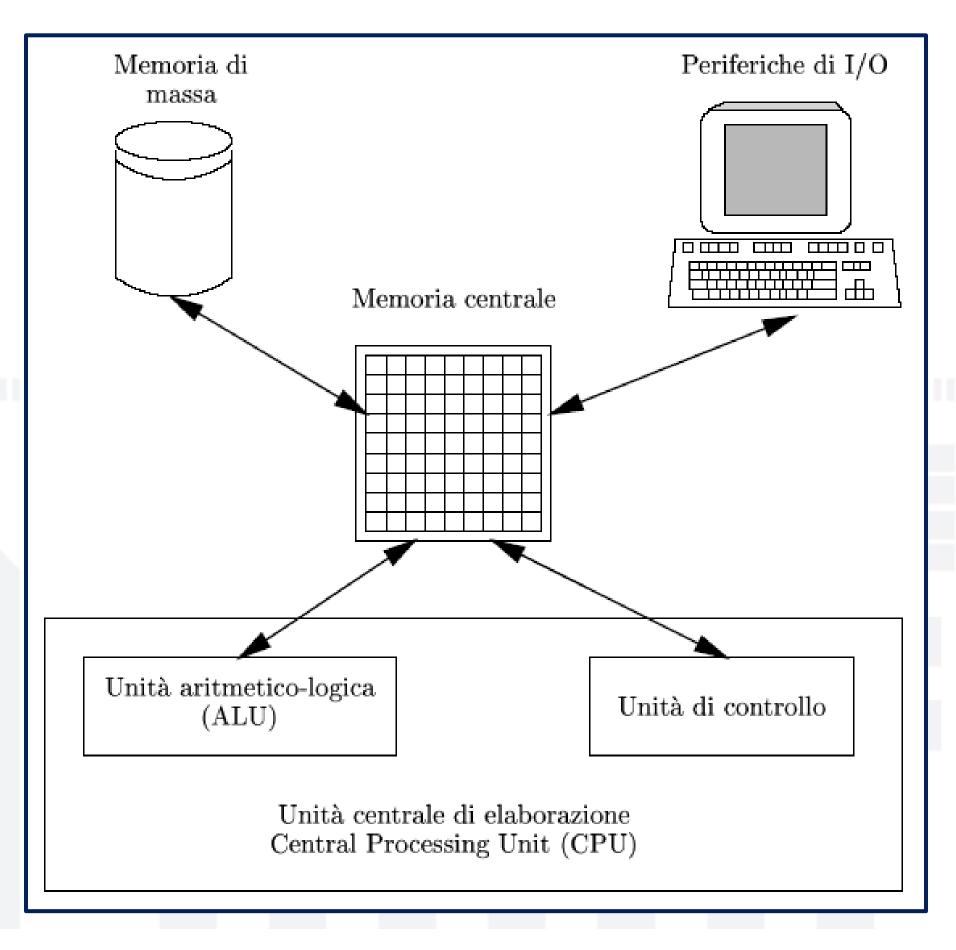

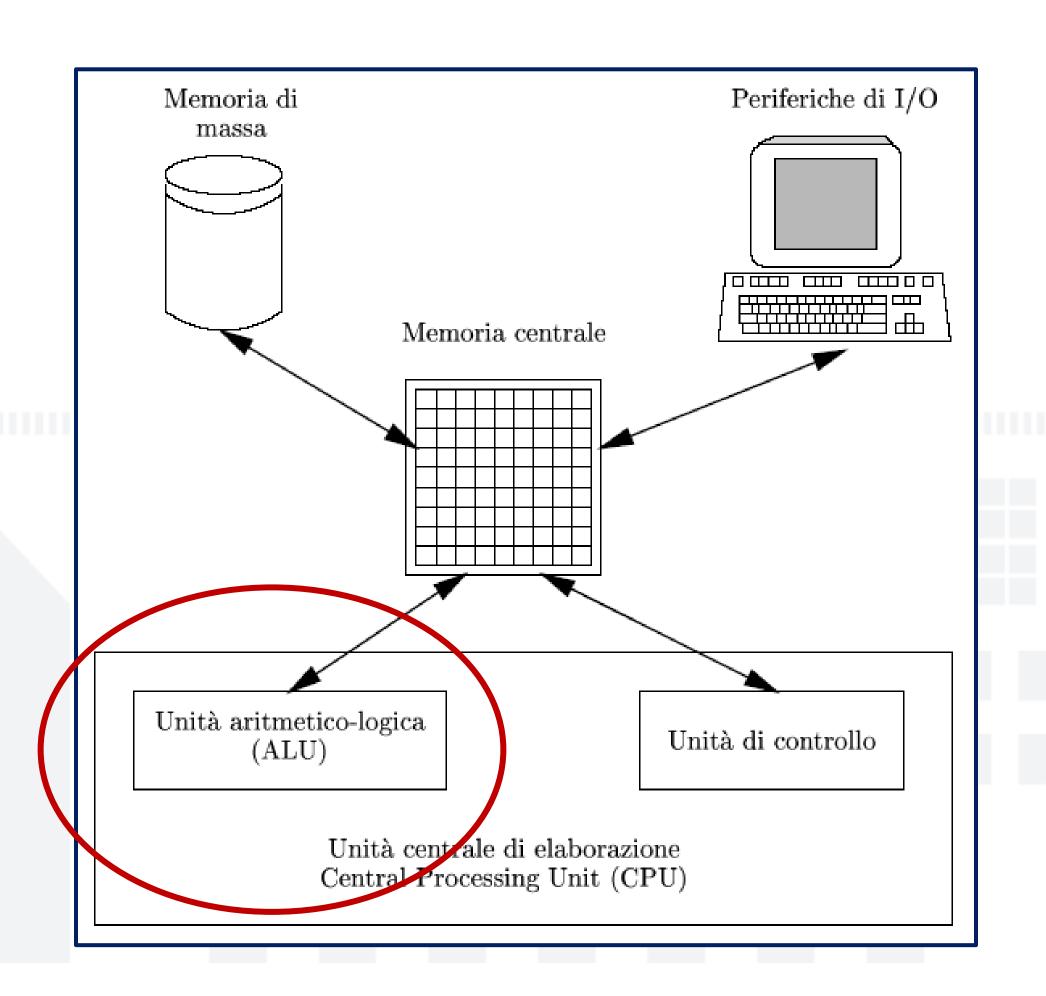

Le varie parti dell'architettura devono sincronizzare le proprie attività:

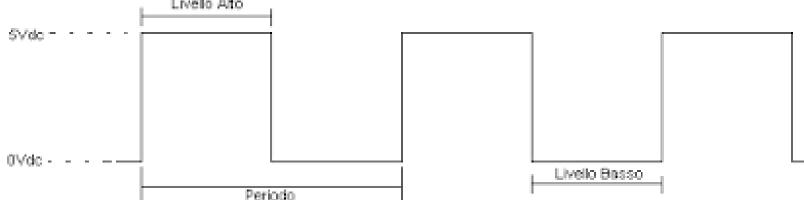

serve un «CLOCK»

E' un segnale periodico.

Più è veloce, più attività si possono fare nell'unità di tempo!

$1GHz = 10^9 Hz$

# Quanto «dura» un'istruzione?

Durata in secondi? minuti? millisecondi? microsecondi?

# 3 GRANDI DOMANDE

1.Come posso rappresentare l'informazione nel pc?

2. Come posso realizzare fisicamente tale rappresentazione?

3. Come posso costruire il pc a partire dagli elementi di base?

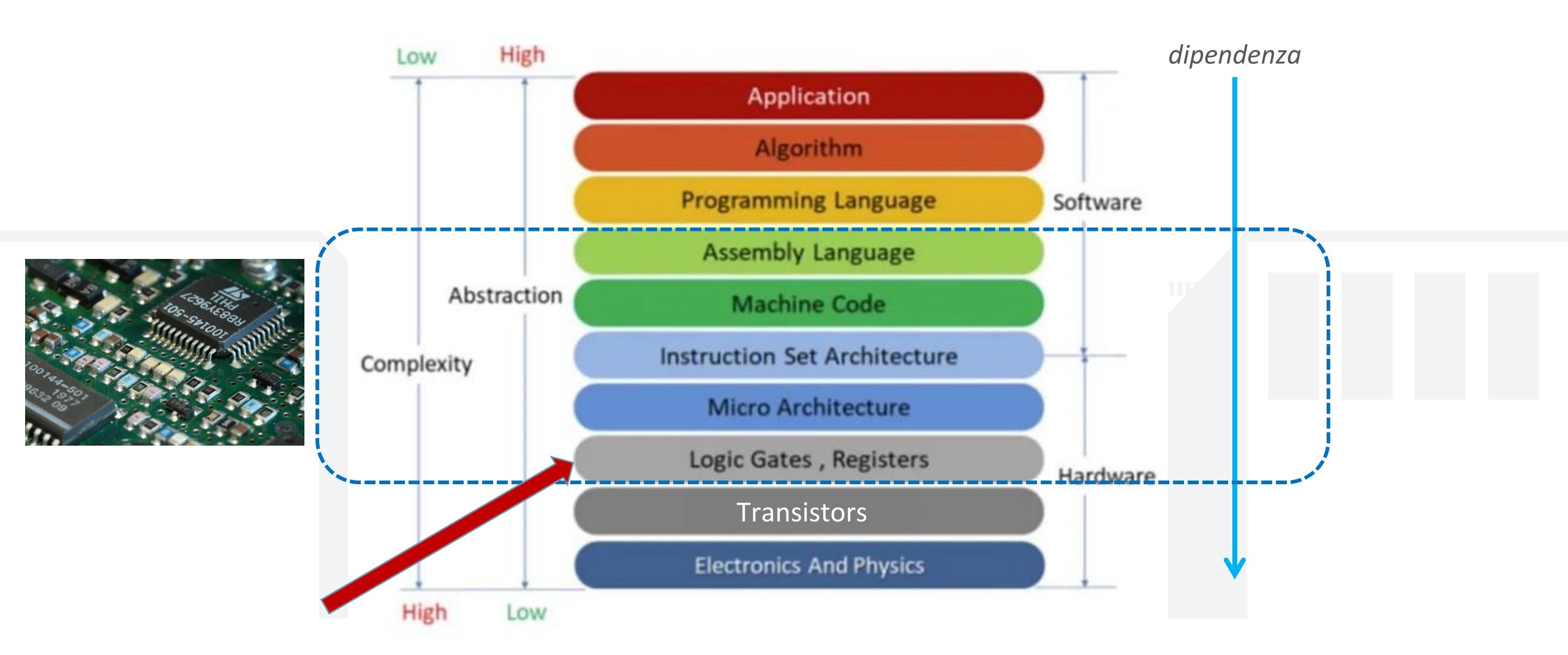

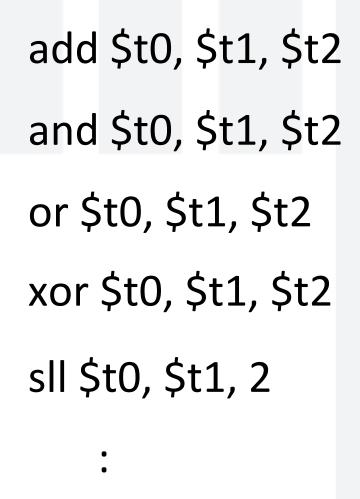

# INSTRUCTION SET ARCHITECTURE

# ARITHMETIC-LOGIC UNIT (ALU)

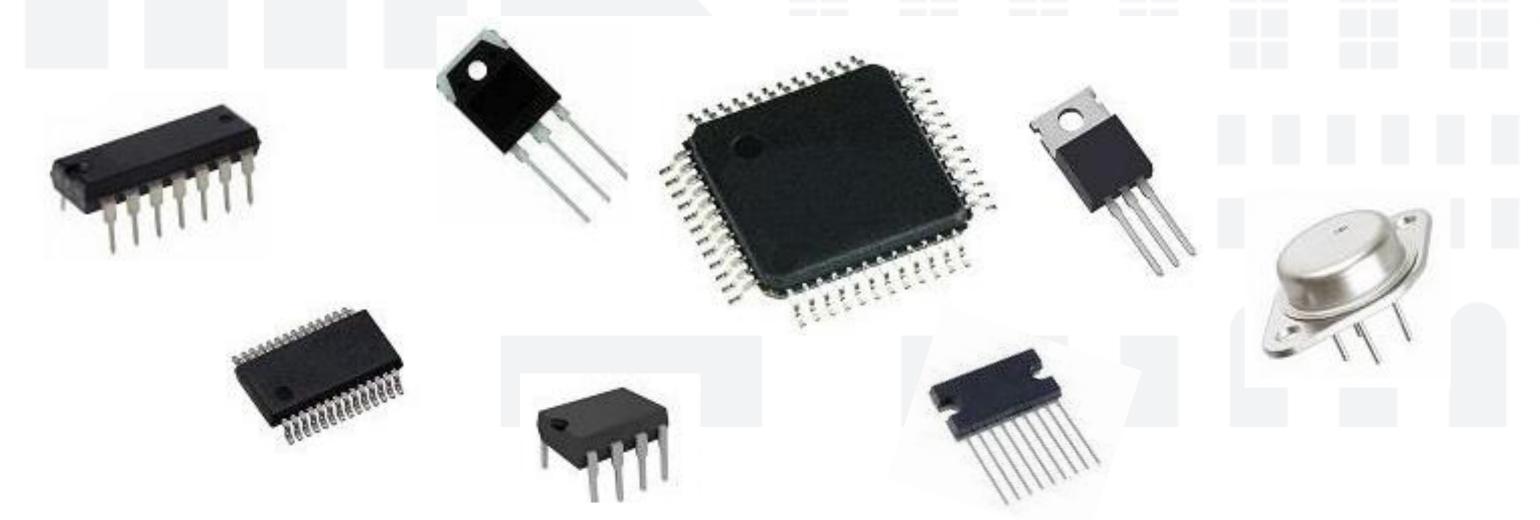

Realizziamo su silicio (elettronica) CIRCUITI LOGICI!

# CIRCUITI LOGICI: INTRODUZIONE

I circuiti logici sono realizzati come circuiti integrati su chip di silicio (piastrina)

• Porte (gate) e fili depositati su chip di silicio, inseriti in un package e collegati all'esterno con un certo insieme di pin (piedini)

• I circuiti integrati si distinguono per grado di integrazione

• Da singole porte indipendenti a circuiti più complessi

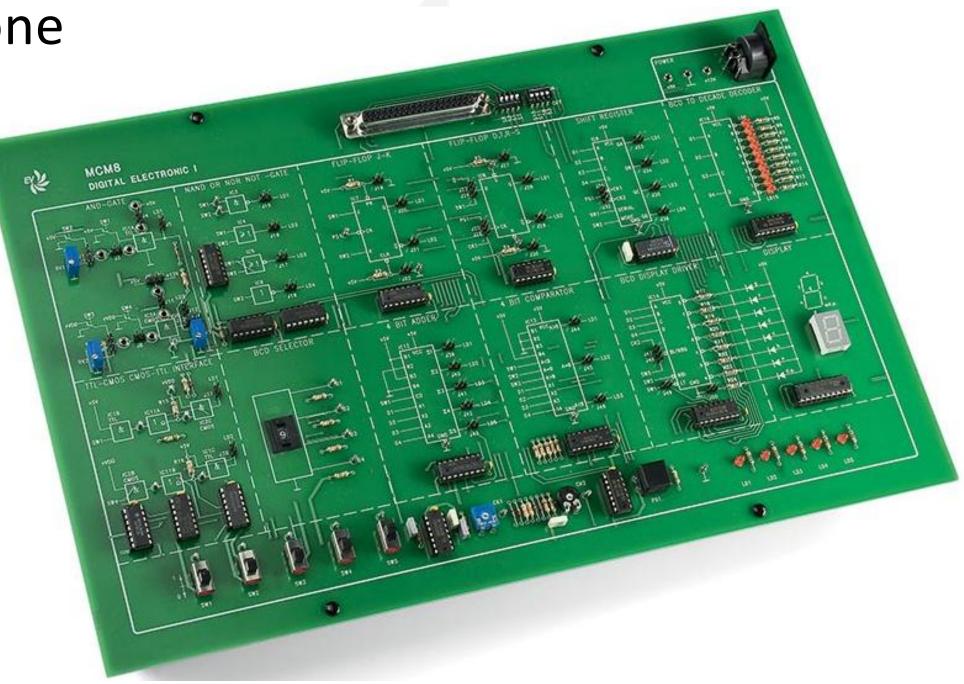

#### CIRCUITI LOGICI: INTEGRAZIONE

- Integrazione

- SSI (Small Scale Integrated): 1-10 porte

- MSI (Medium Scale Integrated): 10-100 porte

- **LSI (Large Scale Integrated):** 100-100.000 porte

- VLSI (Very Large Scale Integrated): > 100.000 porte

- Con SSI, i circuiti integrati contenevano poche porte, direttamente collegate ai pin esterni

- Con tecnologia MSI, i circuiti integrati contenevano alcuni componenti base

- circuiti comunemente usati nel progetto di un computer

- Con tecnologia VLSI, i circuiti integrati possono oggi contenere una CPU completa (o più)

- microprocessore

# CIRCUITI LOGICI

Nell'elettronica digitale sia gli ingressi che le uscite possono assumere solo i valori di segnale alto (1 per convenzione) o basso (0 per convenzione).

In un circuito digitale i valori binari sono ottenuti tramite discretizzazione dei segnali:

Falso: segnali con voltaggio basso <= 1

Vero: segnali con voltaggio più alto >1

- Un circuito (o rete) combinatoria è quel circuito il cui lo stato delle uscite dipende solo dalla funzione logica applicata allo stato istantaneo (cioè in un determinato istante di tempo) delle sue entrate.

- Un circuito (o rete) sequenziale è quel circuito il cui lo stato delle uscite non dipende solo dalla funzione logica applicata ai suoi ingressi, ma anche sulla base di valori pregressi collocati in memoria.

#### PORTE LOGICHE

- Le porte logiche sono i componenti elettronici che permettono di svolgere le operazioni logiche primitive oltre che a quelle direttamente derivate.

- Le porte logiche che realizzano le operazioni principali dell'algebra booleana

- Una porta logica è un circuito elettronico che, dati dei segnali 0 e 1 in input, produce un segnale in output ottenuto effettuando una operazione booleana sugli ingressi

- Le porte logiche hanno n input e generalmente 1 output

- · A ogni combinazione di valori in ingresso corrisponde una e solo una combinazione in di valori uscita

- Dati gli input, l'output corrispondente appare quasi istantaneamente

- Porte logiche fondamentali: AND, OR, NOT

- Porte logiche derivate: NAND, NOR, XOR

# PORTA LOGICA AND

La porta logica AND svolge l'operazione logica di AND tra due bit, detta anche prodotto logico.

Considerando due entrate A e B, l'uscita A · B è data da:

# PORTA LOGICA OR

La porta logica OR svolge l'operazione logica di OR tra due bit, detta anche somma logica.

Considerando due entrate A e B, l'uscita A · B è data da:

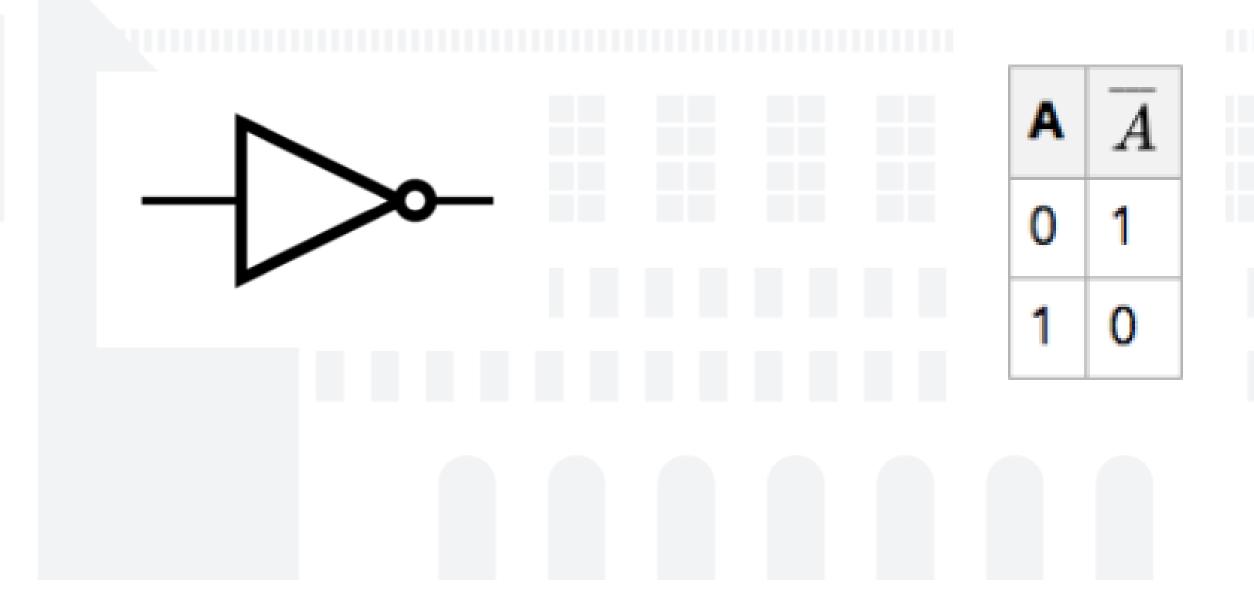

# PORTA LOGICA NOT

La porta logica NOT svolge l'operazione logica di NOT su un bit, detta anche negazione logica.

Considerando un'entrata A, l'uscita Ā è data da:

### PORTE LOGICHE DERIVATE

Oltre alle porte logiche fondamentali (AND, OR, NOT) esistono altre porte che sono realizzate combinando le porte fondamentali, il cui principale scopo è la semplificazione dei circuiti (realizzando operazioni composte in un unico componente).

• Le porte logiche derivate sono NAND, NOR e XOR.

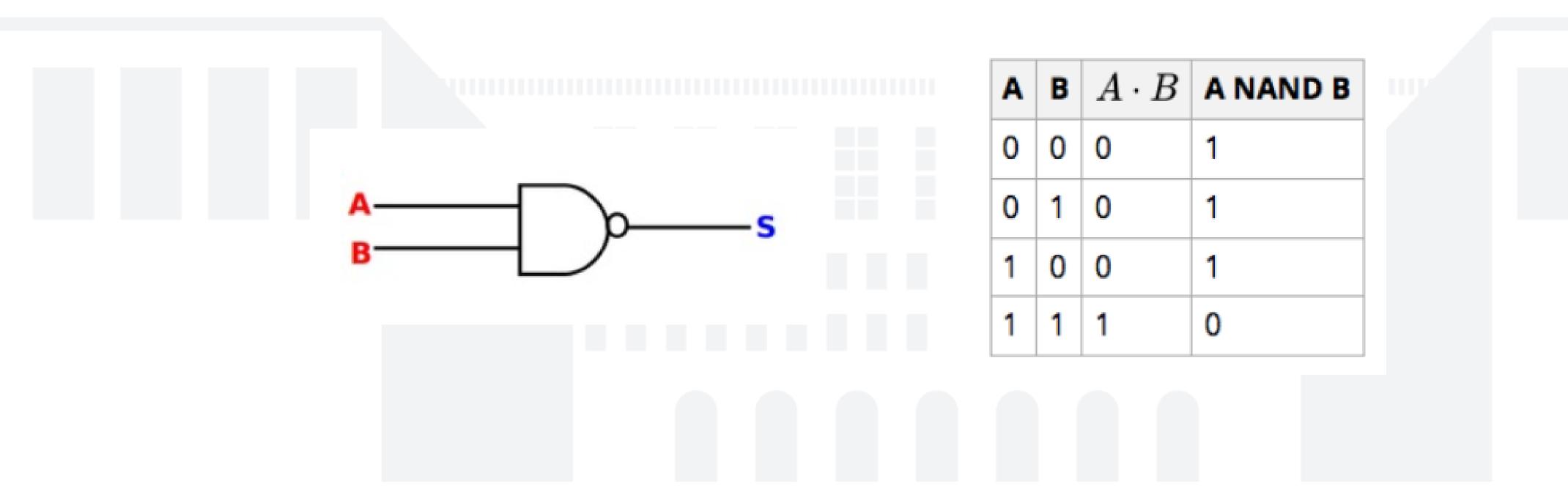

# PORTA LOGICA NAND

La porta logica NAND svolge l'operazione logica di NOT sul bit risultante dall'operazione AND sui bit in ingresso.

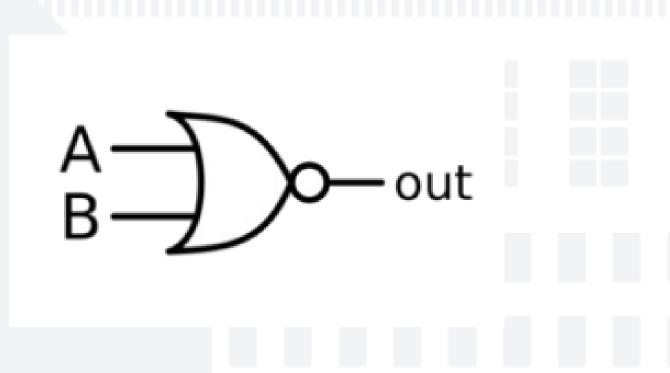

# PORTA LOGICA NOR

La porta logica NOR svolge l'operazione logica di NOT sul bit risultante dall'operazione AND sui bit in ingresso.

| A | В | A + B | A NOR B |

|---|---|-------|---------|

| 0 | 0 | 0     | 1       |

| 0 | 1 | 1     | 0       |

| 1 | 0 | 1     | 0       |

| 1 | 1 | 1     | 0       |

# PORTA LOGICA XOR

La porta logica XOR opera come disgiunzione esclusiva tra due input.

| A | В | A XOR B |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

Funzione logica:

$$\mathbf{A} \oplus \mathbf{B} = \operatorname{not}(\mathbf{A}) \cdot \mathbf{B} + \mathbf{A} \cdot \operatorname{not}(\mathbf{B})$$

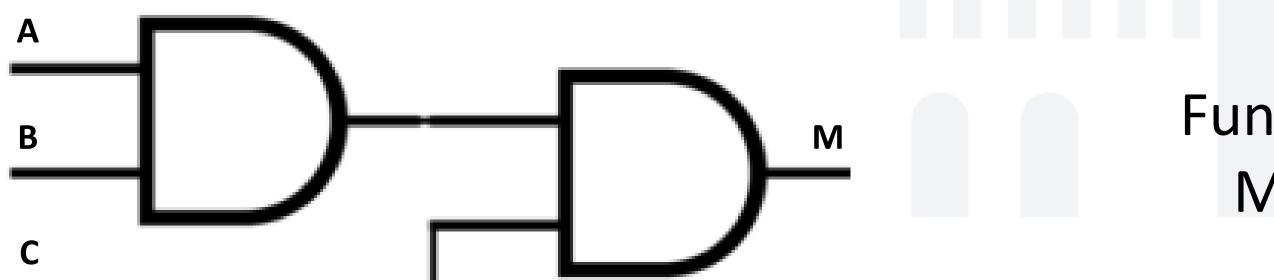

# PORTE CON PIÙ DI DUE INGRESSI

- Ad eccezione della porta NOT, le altre porte logiche possono esistere anche ad N ingressi (2, 3, 4,...,N).

- Queste porte svolgono l'operazione logica associata su N bit invece che su 2.

- > sono particolarmente comode nella rappresentazione grafica dei circuiti logici.

- Nella pratica, cioè nella realizzazione di circuiti, se si hanno a disposizione solo porte a 2 ingressi, è possibile realizzare porte a N ingressi collegando a cascata tra loro porte a 2 ingressi.

- Esempio: una AND a 3 ingressi si può creare usando 2 AND a 2 ingressi come segue:

Funzione logica:

$M = A \cdot B \cdot C$

# OSSERVAZIONI

Qualunque funzione logica può essere costruita usando le porte logiche AND, OR e NOT.

Le porte NOR e NAND svolgono la funzione di inverter e sono definite universali.

NAND -> OR

A NAND  $B = NOT(A \cdot B) = (NOT A) + (NOT B)$

La porta NAND si può quindi realizzare anche con una NOT e un AND in cascata, oppure con due NOT e una OR.

NAND > NOT

A NAND  $1 = NOT(A \cdot 1) = (NOT A)$

Quando uno dei due ingressi alla NAND è 1, allora la porta equivale a negare l'altro input. In tal caso basta una porta NOT.

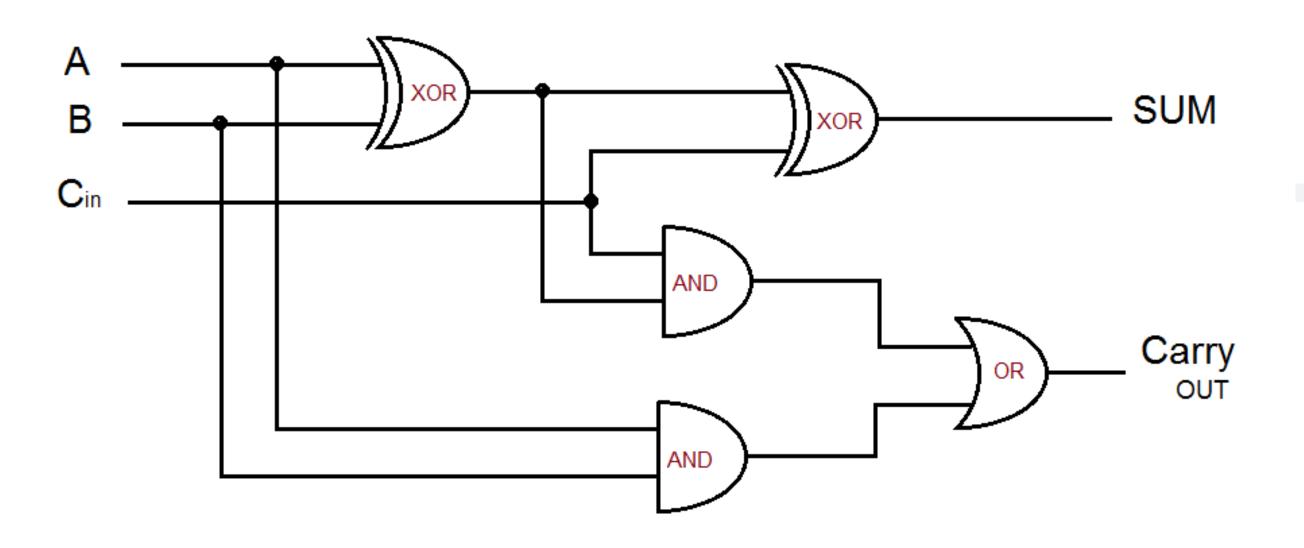

#### **Full adder**

| ] | nput | s                 | Out | tputs        |  |

|---|------|-------------------|-----|--------------|--|

| A | B    | $C_{\mathrm{in}}$ | S   | $C_{ m out}$ |  |

| 0 | 0    | 0                 | 0   | 0            |  |

| 0 | 0    | 1                 | 1   | 0            |  |

| 0 | 1    | 0                 | 1   | 0            |  |

| 0 | 1    | 1                 | 0   | 1            |  |

| 1 | 0    | 0                 | 1   | 0            |  |

| 1 | 0    | 1                 | 0   | 1            |  |

| 1 | 1    | 0                 | 0   | 1            |  |

| 1 | 1    | 1                 | 1   | 1            |  |

Questo circuito realizza la SOMMA BINARIA tra due bit (con riporto).

# PROPRIETA', ASSIOMI E TEOREMI DELL'ALGEBRA BOOLEANA

L'algebra di Boole (anche detta algebra booleana, logica booleana o reticolo booleano), in matematica e logica matematica, è il ramo dell'algebra in cui le variabili possono assumere solamente i valori vero e falso (valori di verità), generalmente denotati rispettivamente come 1 e 0.

| N° | Nome                      | Proprietà                                            | h |

|----|---------------------------|------------------------------------------------------|---|

| 1  | Proprietà associativa     | a + (b + c) = (a + b) + c; a · (b · c) = (a · b) · c |   |

| 2  | Proprietà commutativa     | a + b = b + a; a · b = b · a                         |   |

| 3  | Proprietà distributiva    | a+(b·c)=(a+b)·(a+c)<br>a·(b+c)=(a·b)+(a·c)           |   |

| 4  | Assioma dell'annullamento | a · 0 = 0; a + 1 = 1                                 |   |

| 5  | Assioma del Complemento   | $(a + \bar{a}) = 1; (a \cdot \bar{a}) = 0$           |   |

| 6  | Assioma dell'idempotenza  | a · a = a; a + a = a                                 |   |

| 7  | Assioma doppia negazione  | ā = a                                                |   |

| 8  |                           |                                                      | l |

|    | Teorema di DeMorgan       | a + b = ā · b ; a · b = ā + b                        |   |

| 9  | Teorema dell'assorbimento | Se Y = a + ab allora Y = a                           |   |

| 10 | Teorema del consenso      | Se Y = ab + āc + bc allora Y = ab + āc               |   |

https://it.wikipedia.org/wiki/Algebra\_di\_Boole

# Leggi di De Morgan

$$\overline{a+b} = \overline{a} \cdot \overline{b}$$

$$\overline{a \cdot b} = \overline{a} + \overline{b}$$

# TEOREMA DI ESPRESSIONE CANONICA (O DEI MINTERMINI)

Qualunque funzione logica può essere costruita usando le porte logiche AND, OR e NOT.

Il Teorema dei Mintermini afferma che ogni funzione booleana può essere espressa come una somma (operazione OR) di mintermini.

Un **mintermine** è un prodotto (operazione AND) di tutte le variabili della funzione, ciascuna presente in forma diretta o negata, che rendono la funzione uguale a 1.

In altre parole, <u>per ogni combinazione di variabili in cui la funzione booleana restituisce 1</u>, esiste un mintermine corrispondente. La somma di tutti questi mintermini fornisce una rappresentazione completa della funzione, nota come <u>prima forma canonica o forma normale disgiuntiva</u> (Sum of Products, SOP).

È un **modo standard per rappresentare una funzione logica** usando solo AND (prodotto logico), OR (somma logica), NOT (negazione).

# TEOREMA DI ESPRESSIONE CANONICA DUALE (O DEI MAXTERMINI)

Qualunque funzione logica può essere costruita usando le porte logiche AND, OR e NOT.

Il Teorema dei Maxtermini afferma che ogni funzione booleana può essere espressa come un prodotto (operazione AND) di maxtermini.

Un maxtermine è una somma (operazione OR) di tutte le variabili della funzione, ciascuna presente in forma diretta o negata, che rendono la funzione uguale a 0.

In altre parole, <u>per ogni combinazione di variabili in cui la funzione booleana restituisce 0</u>, esiste un maxtermine (somma) corrispondente. La somma di tutti questi maxtermini fornisce una rappresentazione completa della funzione, nota come seconda forma canonica o forma normale congiuntiva (Product of Sums, POS).

È un altro modo standard per rappresentare una funzione logica usando solo AND (prodotto logico), OR (somma logica), NOT (negazione).

#### Full adder

| ] | nput | ts Outputs        |   | tputs |                                   |

|---|------|-------------------|---|-------|-----------------------------------|

| A | B    | $C_{\mathrm{in}}$ | S |       |                                   |

| 0 | 0    | 0                 | 0 |       |                                   |

| 0 | 0    | 1                 | 1 |       |                                   |

| 0 | 1    | 0                 | 1 |       | Ogni riga della tabella di verità |

| 0 | 1    | 1                 | 0 |       | genera un MINTERMINE.             |

| 1 | 0    | 0                 | 1 |       |                                   |

| 1 | 0    | 1                 | 0 |       |                                   |

| 1 | 1    | 0                 | 0 |       |                                   |

| 1 | 1    | 1                 | 1 |       |                                   |

A seconda di quale forma del *Teorema dei Mintermini* usiamo, dobbiamo formare i mintermini e poi combinarli tra loro in modo diverso.

- (1)Nel caso della forma SOP, cerchiamo le righe dove S=1, formiamo i mintermini come prodotto delle variabili e poi li sommiamo.

- (2)Nel caso della forma POS, cerchiamo le righe dove S=0, i mintermini sono somma delle variabili e vengono moltiplicati tra loro.

#### Full adder

Considerando la forma SOP del Teorema.. (continua..)

|   | Inputs Outputs |   | tputs             |   |  |                               |

|---|----------------|---|-------------------|---|--|-------------------------------|

|   | A              | B | $C_{\mathrm{in}}$ | S |  |                               |

|   | 0              | 0 | 0                 | 0 |  |                               |

| Ш | 0              | 0 | 1                 | 1 |  | $not(A) \cdot not(B) \cdot C$ |

| П | 0              | 1 | 0                 | 1 |  | not(A) · B · not(C)           |

|   | 0              | 1 | 1                 | 0 |  |                               |

|   | 1              | 0 | 0                 | 1 |  | $A \cdot not(B) \cdot not(C)$ |

|   | 1              | 0 | 1                 | 0 |  |                               |

|   | 1              | 1 | 0                 | 0 |  |                               |

|   | 1              | 1 | 1                 | 1 |  | A · B · C                     |

$S = not(A) \cdot not(B) \cdot C + not(A) \cdot B \cdot not(C) + A \cdot not(B) \cdot not(C) + A \cdot B \cdot C$

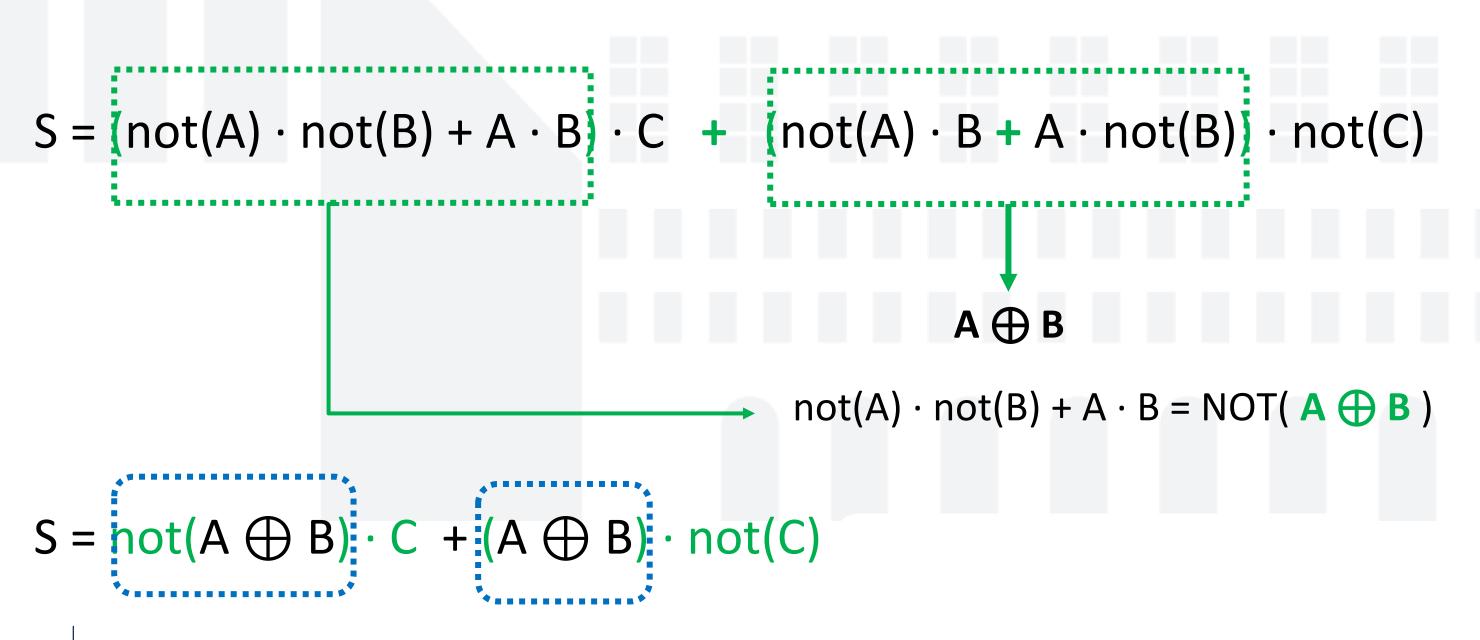

#### Full adder

Considerando la forma SOP del Teorema.. (continua..)

$$S = not(A) \cdot not(B) \cdot C + not(A) \cdot B \cdot not(C) + A \cdot not(B) \cdot not(C) + A \cdot B \cdot C$$

pr. distrib. inversa

| A | В | A XOR B | NOT(A XOR B) |

|---|---|---------|--------------|

| 0 | 0 | 0       | 1            |

| 0 | 1 | 1       | 0            |

| 1 | 0 | 1       | 0            |

| 1 | 1 | 0       | 1            |

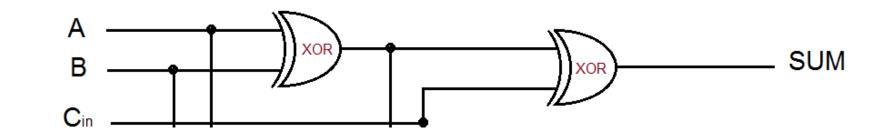

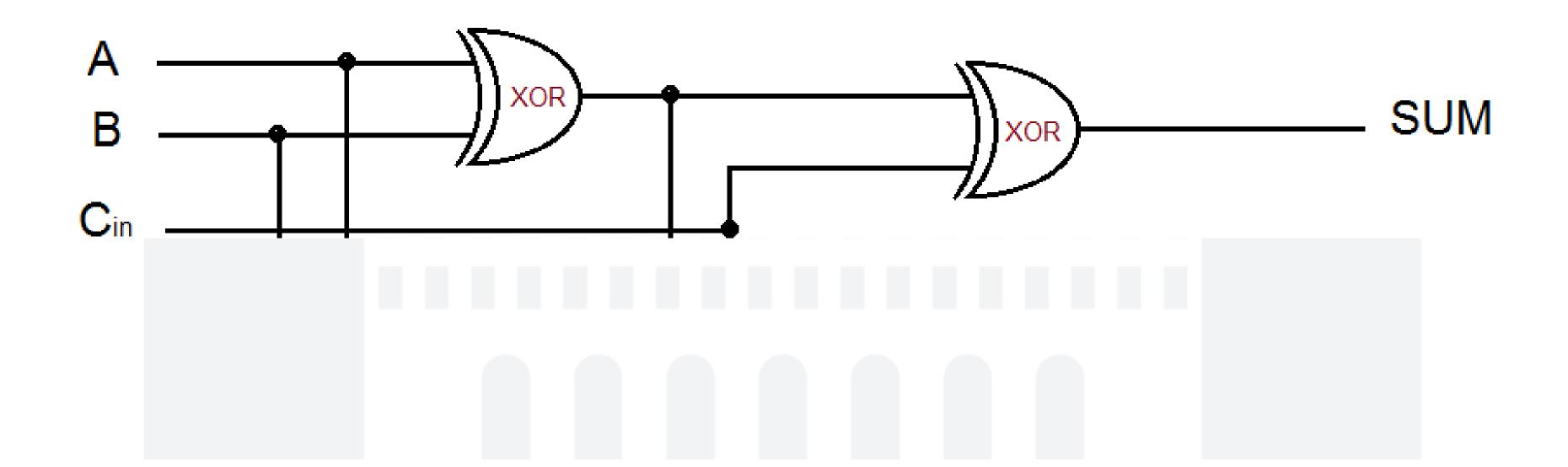

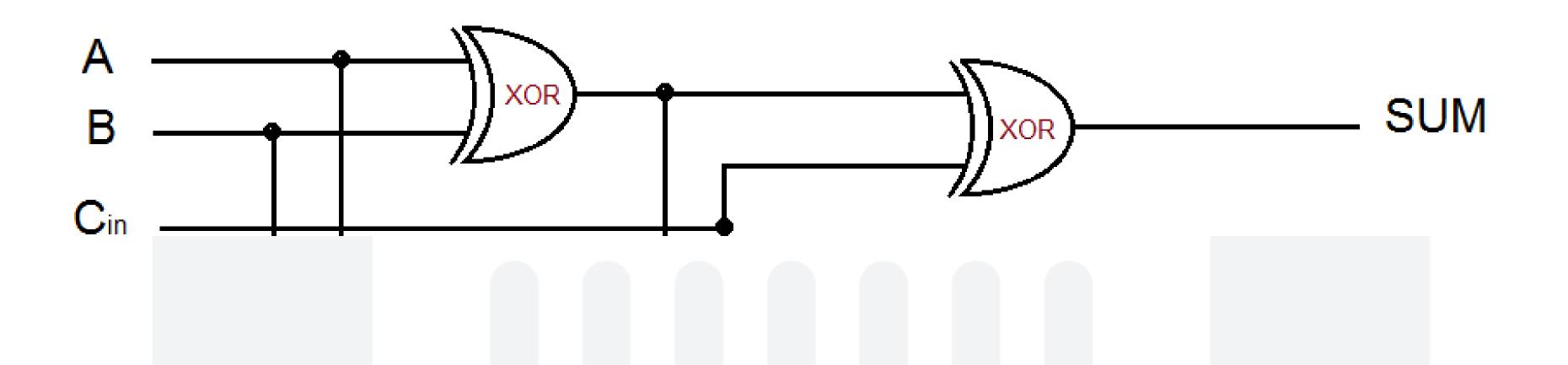

#### Full adder

Considerando la forma SOP del Teorema..

$$S = (A \oplus B) \oplus C$$

#### Full adder

Considerando la forma POS del Teorema.. (continua..)

| Inputs |   | puts Outputs |   | puts |                          |

|--------|---|--------------|---|------|--------------------------|

| A      | B | $C_{ m in}$  | S |      |                          |

| 0      | 0 | 0            | 0 |      | not(A) · not(B) · not(C) |

| 0      | 0 | 1            | 1 |      |                          |

| 0      | 1 | 0            | 1 |      |                          |

| 0      | 1 | 1            | 0 |      | not(A) · B · C           |

| 1      | 0 | 0            | 1 |      |                          |

| 1      | 0 | 1            | 0 |      | A·not(B)·C               |

| 1      | 1 | 0            | 0 |      | A · B · not(C)           |

| 1      | 1 | 1            | 1 |      |                          |

$S = not(A) \cdot not(B) \cdot not(C) + not(A) \cdot B \cdot C + A \cdot not(B) \cdot C + A \cdot B \cdot not(C)$

#### **Full adder**

Considerando la forma POS del Teorema.. (continua..)

$$S = not(A) \cdot not(B) \cdot not(C) + not(A) \cdot B \cdot C + A \cdot not(B) \cdot C + A \cdot B \cdot not(C)$$

=

$$(not(A) \cdot not(B) + A \cdot B) \cdot not(C)$$

+  $(not(A) \cdot B + A \cdot not(B)) \cdot C = (A \oplus B) \oplus C$

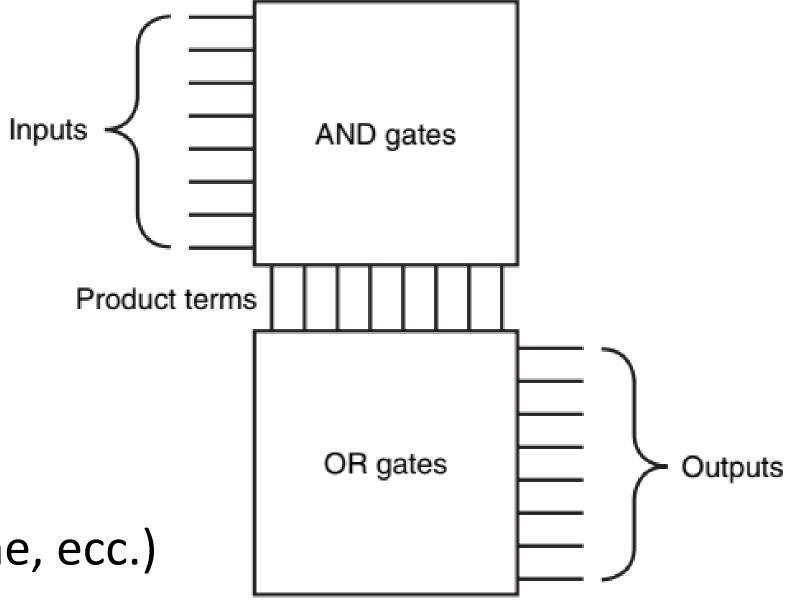

#### LOGICHE A DUE LIVELLI E PLA

Qualunque funzione logica può essere costruita usando porte AND, OR e NOT.

Possiamo creare logiche a due livelli:

- Somma di prodotti: somma logica (OR) di prodotti (AND)

- Prodotto di somme: prodotto (AND) di somme (OR)

# Esempi di uso di circuiti in PLA:

- Circuiti di controllo

- Decoder personalizzati

- Più segnali di uscita da input comuni (es. segnali di stato, di selezione, ecc.)

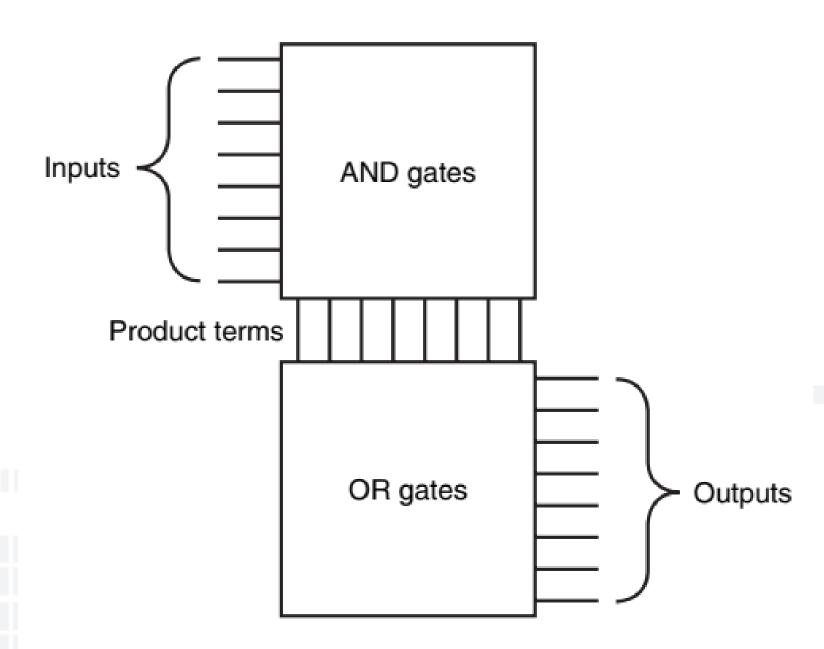

# PROGRAMMABLE LOGICAL ARRAY

Una **PLA** è un circuito logico programmabile che implementa **una o più funzioni booleane** nella forma Somma di Prodotti (SOP):  $F = P_1 + P_2 + \cdots + P_n$  dove ciascun  $P_i$  è un prodotto logico (AND) di input o dei loro complementi.

- Un insieme di **input**

- I corrispondenti input complementati (mediante inverter) per poter gestire più uscite

- Una logica a due stage:

Primo stage: un array di porte logiche AND (prodotto)

Secondo stage: un array di porte logiche OR (somma)

Output: una stessa base di prodotti logici (AND) può essere combinata in modi diversi per produrre diverse funzioni logiche. Ogni uscita può combinare (OR) i prodotti in modo diverso.

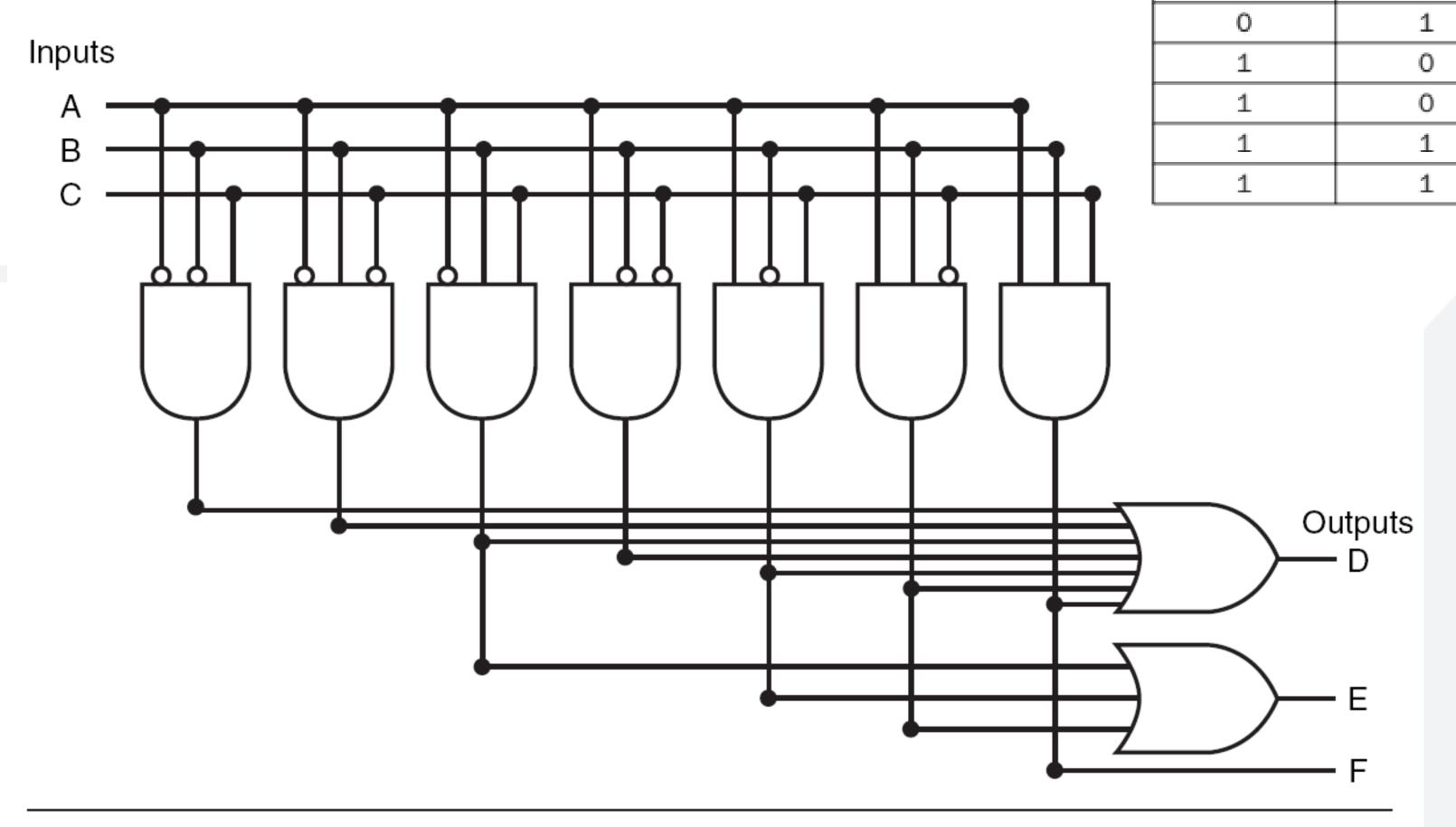

# PLA

#### Esempio

Consideriamo la seguente tabella di verità.

|   | Inputs |   |   | Outputs |   |

|---|--------|---|---|---------|---|

| A | В      | C | D | E       | F |

| 0 | 0      | 0 | 0 | 0       | 0 |

| 0 | 0      | 1 | 1 | 0       | 0 |

| 0 | 1      | 0 | 1 | 0       | 0 |

| 0 | 1      | 1 | 1 | 1       | 0 |

| 1 | 0      | 0 | 1 | 0       | 0 |

| 1 | 0      | 1 | 1 | 1       | 0 |

| 1 | 1      | 0 | 1 | 1       | 0 |

| 1 | 1      | 1 | 1 | 0       | 1 |

Costruire il PLA corrispondente come somme di prodotto

Come si fa?

Si costruisce la SOP per ogni colonna. Si tratta ogni colonna come una funzione logica indipendente.

# PLA

# Esempio

FIGURE C.3.4 The PLA for implementing the logic function described in the example.

Inputs

В

C

A

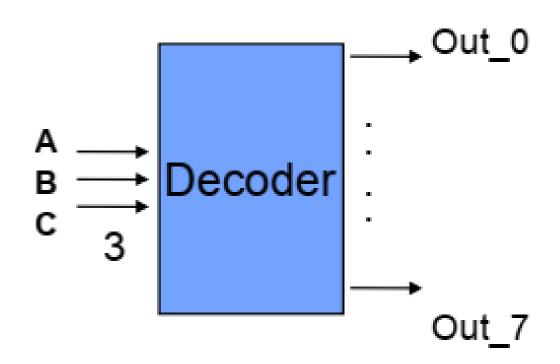

# DECODER (1/2)

Un decoder è un componente elettronico caratterizzato dall'avere n ingressi e 2<sup>n</sup> uscite.

Lo scopo del decoder è di **impostare allo stato alto l'uscita corrispondente alla conversione in base 10** della codifica binaria a n bit ricevuta **in input** (e di impostare allo stato basso tutte le altre).

# In pratica:

- gli n input sono interpretati come un numero unsigned

- se questo numero rappresenta il numero i, allora

- solo il bit in output di indice i (i=0,1,...,2<sup>n-1</sup>) verrà posto ad 1

- tutti gli altri verranno posti a 0

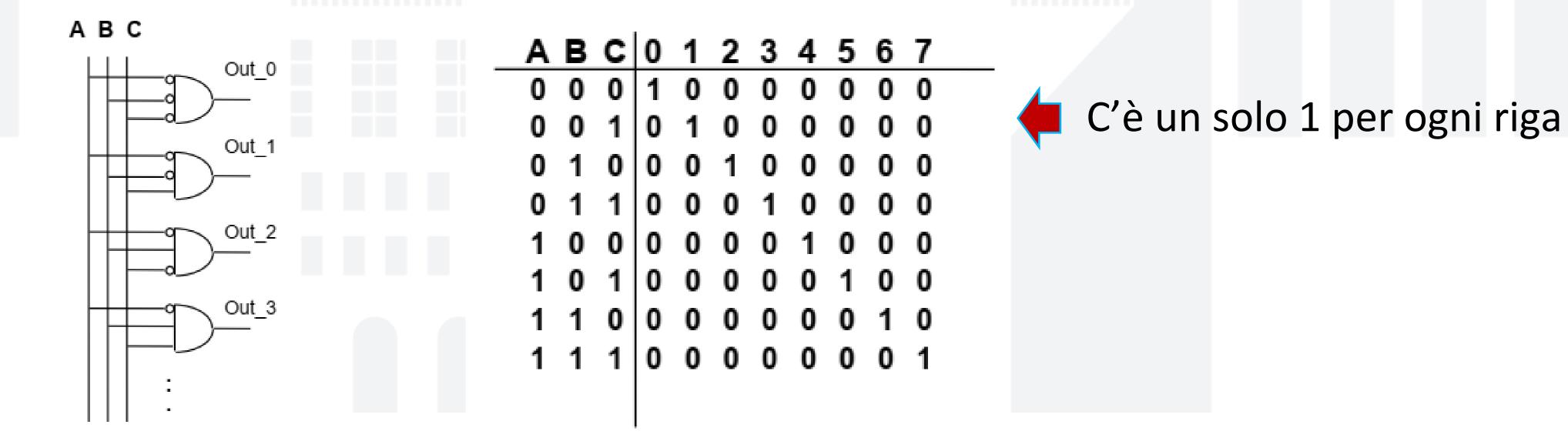

# DECODER (2/2)

2<sup>n</sup> uscite, solo 1 valore è attivo per ogni combinazione di input.

#### Quindi:

- l'ingresso seleziona una delle uscite;

- l'uscita selezionata ha valore 1 tutte le altre 0

Con 3 bit possiamo selezionare UNA di  $2^3$  = 8 uscite

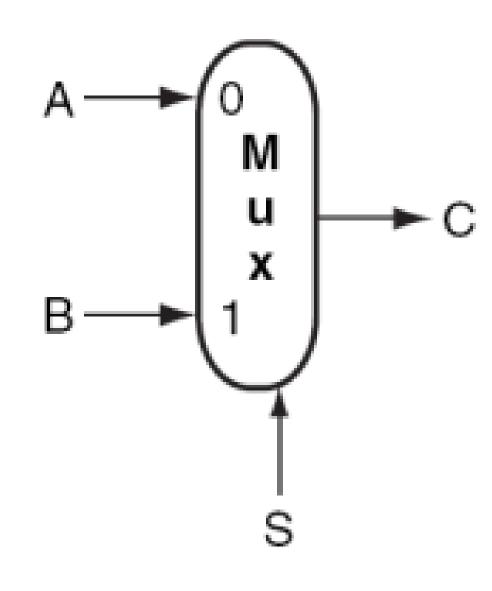

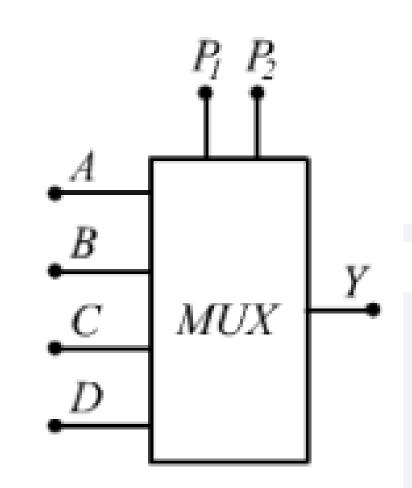

Un multiplexer, detto anche selettore, è un componente elettronico caratterizzato da:

- 2<sup>n</sup> entrate principali

- n entrate di controllo (selettore)

- 1 uscita

Il valore del selettore determina quale input diviene output.

#### Esempio 1

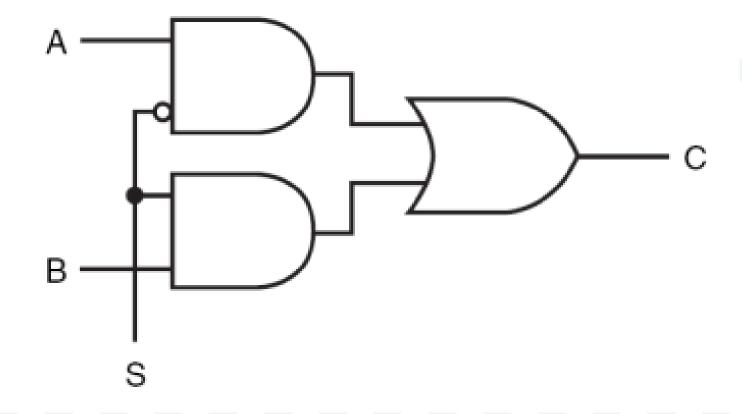

Funzione logica

$$C = (A \cdot \bar{S}) + (B \cdot S)$$

### Qual è la tabella di verità di questo circuito?

Circuito logico equivalente

S ha la funzione di segnale di controllo

| S | A | В | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

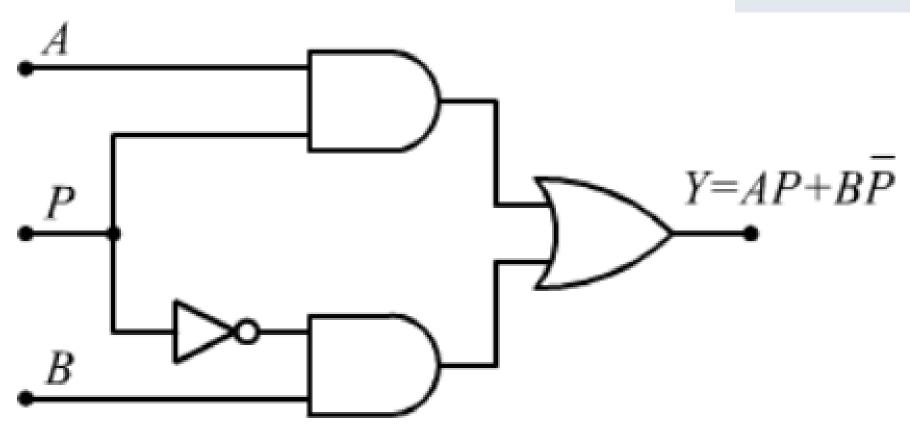

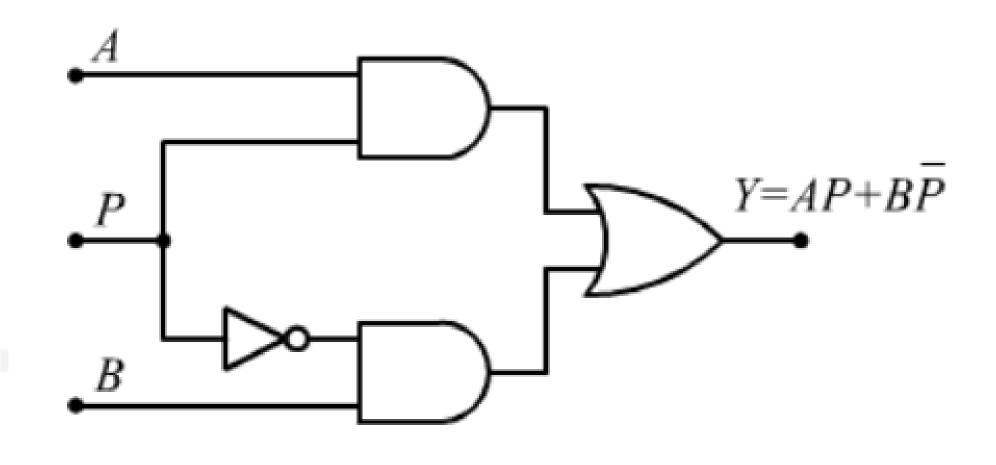

## Esempio 2

Circuito logico equivalente

**Nota**. Questo circuito è equivalente al precedente, ma il controllo dato dal segnale P è invertito rispetto a prima. In questo caso, se P=1, viene abilitato l'ingresso A.

$$A=0, B=0, P=0$$

$$0 \text{ OR } 0 >> 0$$

$$A=1, B=0, P=0$$

$$0 \text{ OR } 0 >> 0$$

$$A=1, B=1, P=0$$

$$0 \text{ OR } 1 >> 1$$

$$A=0, B=1, P=0$$

$$0 \text{ OR } 1 >> 1$$

# Esempio 2

Circuito logico equivalente

#### Tabella di verità

$$egin{array}{c|c} P & Y \\ \hline 0 & B \\ I & A \\ \hline \end{array}$$

$$A=0, B=0, P=1$$

$$0 \text{ OR } 0 >> 0$$

$$1 \text{ OR } 0 >> 1$$

$$A=0, B=1, P=1$$

$$0 \text{ OR } 1 >> 1$$

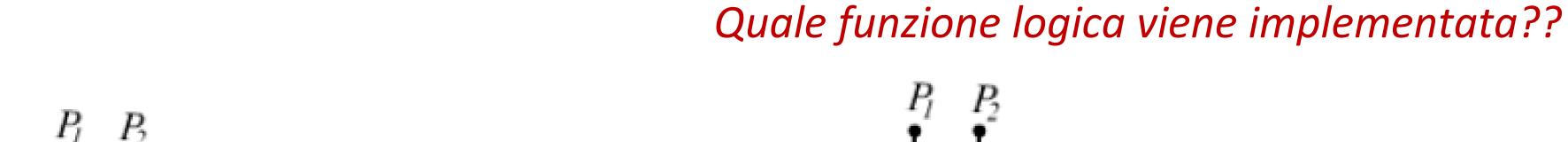

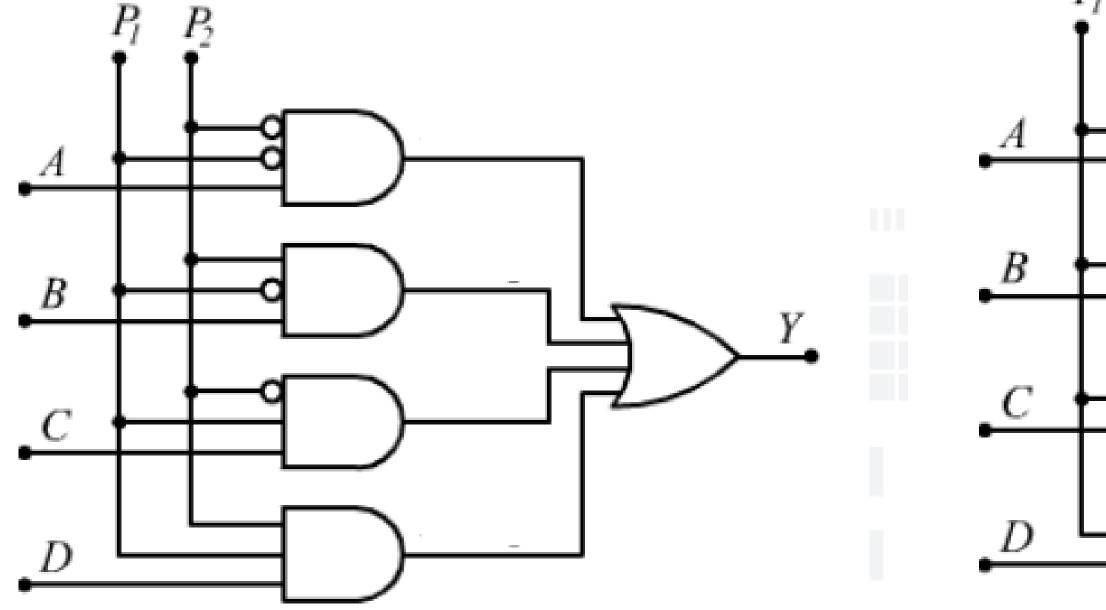

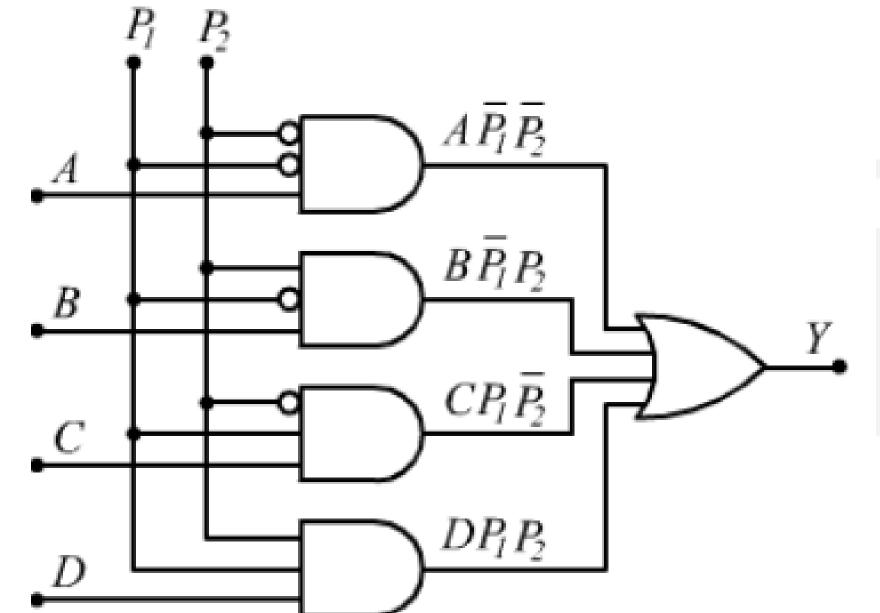

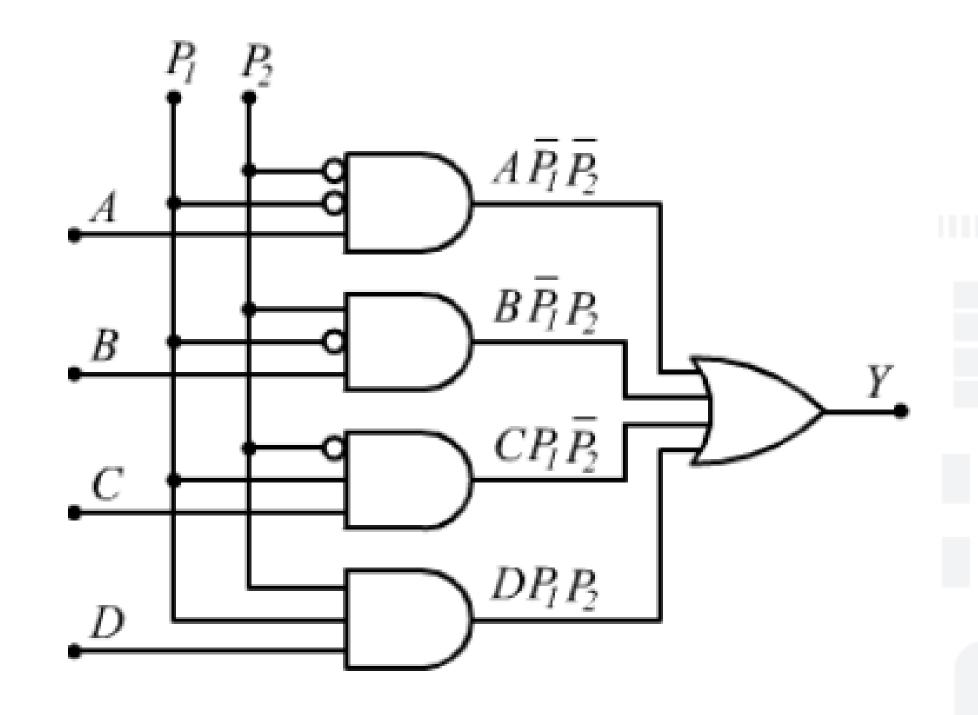

# Esempio 3

Circuito logico

$$Y = A\bar{P}_1\bar{P}_2 + B\bar{P}_1P_2 + CP_1\bar{P}_2 + DP_1P_2$$

#### Esempio 3

$$Y = A\bar{P}_1\bar{P}_2 + B\bar{P}_1P_2 + CP_1\bar{P}_2 + DP_1P_2$$

Tabella di verità

| $P_{l}$ | $P_2$    | Y |

|---------|----------|---|

| 0       | $\theta$ | A |

| 0       | 1        | B |

| I       | 0        | C |

| I       | 1        | D |

Circuito con 2 segnali di controllo

# Materiale per la lezione

Appendice B, Patterson & Hennessy