## **MEMORIE**

Una panoramica sulle tipologie e sulle caratteristiche dei dispositivi di memoria

# **Tipologie**

- RAM

- Statiche

- Dinamiche

- ROM

- A maschera

- PROM

- EPROM

- EEPROM o EAROM

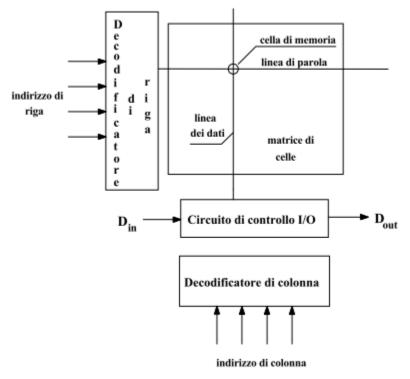

#### **Struttura Base**

- Serie di CELLE di memoria

- Decoder degli indirizzi

- Circuito di controllo di I/O

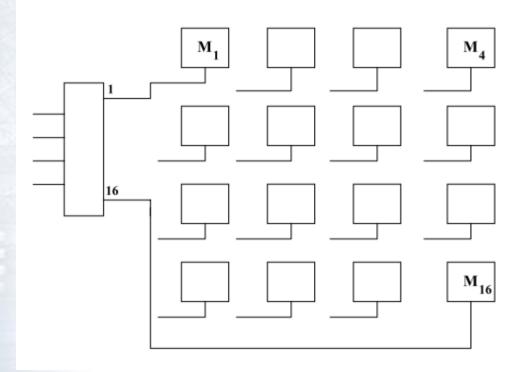

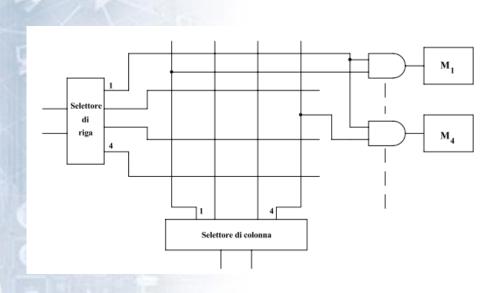

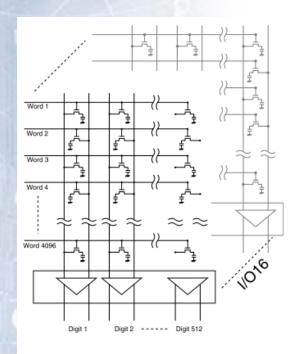

### Indirizzamento a matrice

Per limitare il numero di linee di collegamento e semplificare il circuito è molto impiegato l'indirizzamento a matrice

# Segnali tipici

- Address: [A0..An]

- Data: I/O [D0..Dm]

- Lettura/Scrittura: R/W (oppure R/nW)

- Chip Select : CS

- Alimentazione e massa: Vcc e Gnd

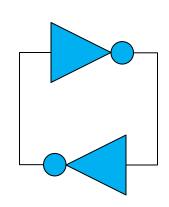

## Cella di SRAM

#### Funzionamento:

Si compone di un circuito bistabile che può essere forzato in uno qualsiasi dei suoi due stati

#### Pregi

- L'informazione rimane stabile (lettura non distruttiva)

- Accesso abbastanza rapido

#### Difetti

- Richiede 6 MOS

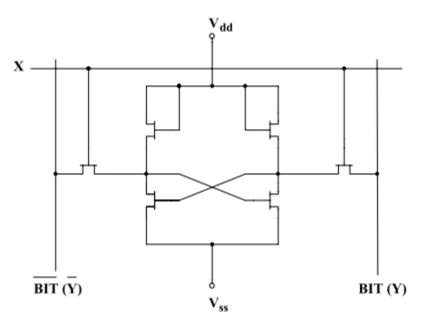

## **Memoria SRAM**

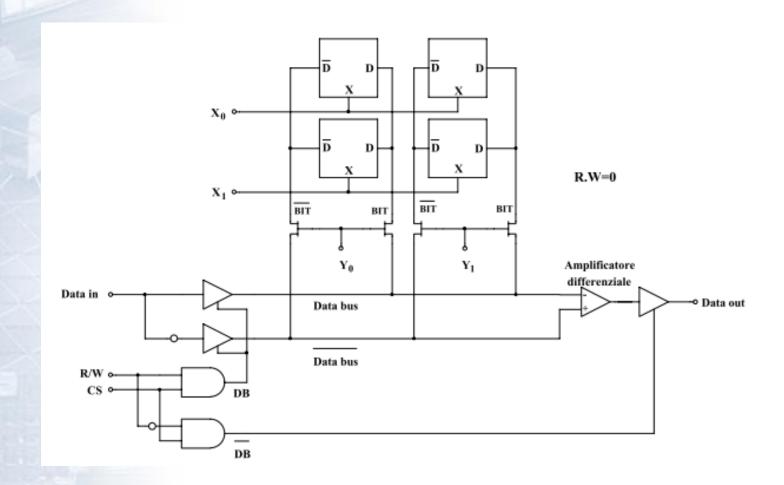

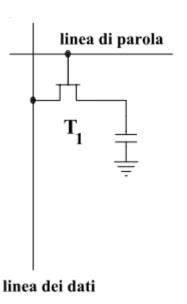

## Cella DRAM

#### Funzionamento:

- Lettura

- Si pone la linea dati a livello alto (precharge)

- Si attiva la linea di parola

- Si analizza la tensione sulla linea dati attraverso un amplificatore a soglia o "sense amplifier"

- Se la tensione cala sotto la soglia : 0

- Se la tensione si manntiene alta : 1

- Si riscrive il dato nella cella

#### Scrittura

- Si attiva la linea di parola

- Sulla linea dati si scrive il valore desiderato

## Cella DRAM

- Pregi:

- Piccola e compatta

- Economica

- Difetti

- La lettura è distruttiva

- La carica di C deve essere ristabilita

- Ad ogni lettura

- Dopo un certo tempo

- Tempi di accesso più lunghi

- Tempi legati alla carica/scarica

- Tempi di refresh

- Precarica del livello di tensione nelle linee

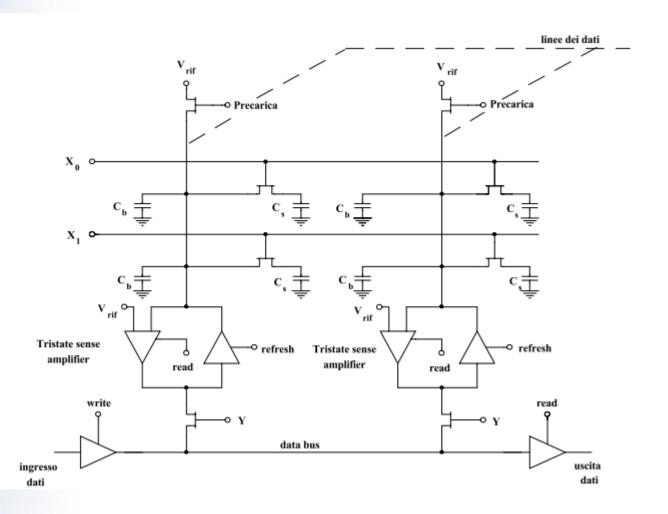

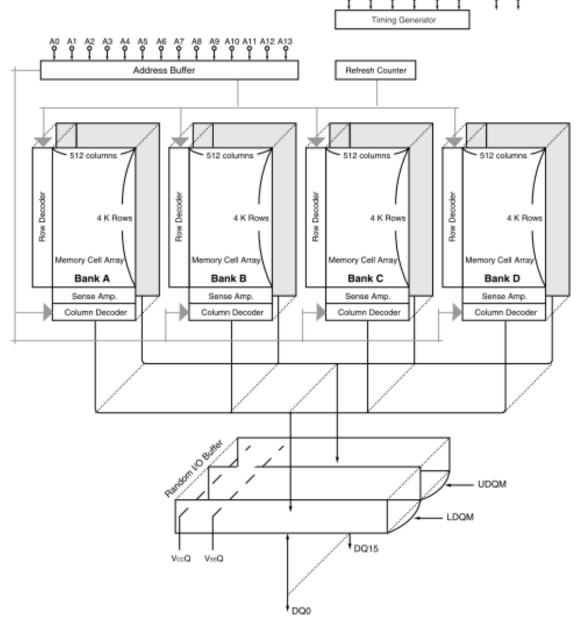

# **Memoria DRAM**

## **Memoria DRAM**

#### Note:

- Precharge

- La lettura del dato di una riga implica il refresh per tutta la riga

- Se una riga non viene letta non c'e' refresh

- Un sistema di controllo (solitamente integrato nel chip) basato su un contatore compie ad istanti regolari un accesso a tutte le righe

- Refresh alla freq. di qualche kHz

#### Migliorie:

- address multiplexing (si sfruttano i medesimi piedini per l'inirizzo di riga prima e di colonna dopo)

- piedini CAS e RAS (Column/Row Access Strobe)

- Lettura in sequenza dei dati di una stessa riga

- Più bit corrispondono a più sistemi in parallelo

# Tipologie principali di DRAM

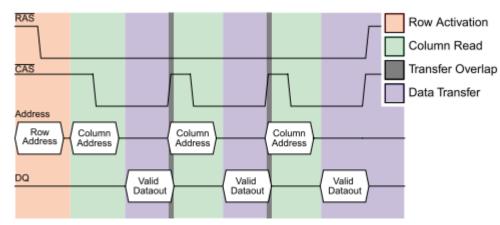

- Fast Page Mode (FPM) DRAM

- Dopo aver attivato una riga si accede sequenzialmente a più dati sulla stessa riga

- Extended data Out (EDO) DRAM

- Simile a FP ma il driver d'uscita è stato modificato per mantenere stabile il valore anche se la linea nCAS torna alta. Lavora secondo una similcircuito sistolico

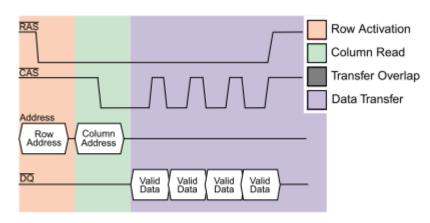

- Burst EDO (BEDO) DRAM

- Burst mode per accedere a più dati in sequenza

- Usa un contatore interno che sveltisce l'accesso sequenziale ai dati

- Si può anticipare l'indirizzo successivo

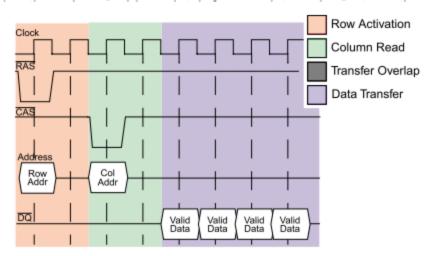

- Synchronous DRAM (SDRAM)

- Dram pilotata da un clock + Burst Mode

- Usa una FSM

- Multi Bank

- Double Data Rate (DDR SDRAM)

- Funzionano tanto sul fronte di salita che di discesa del clock

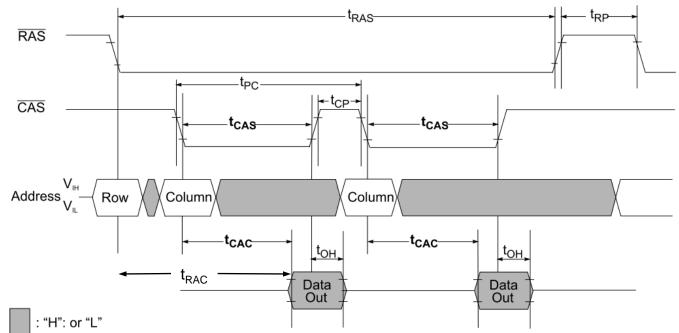

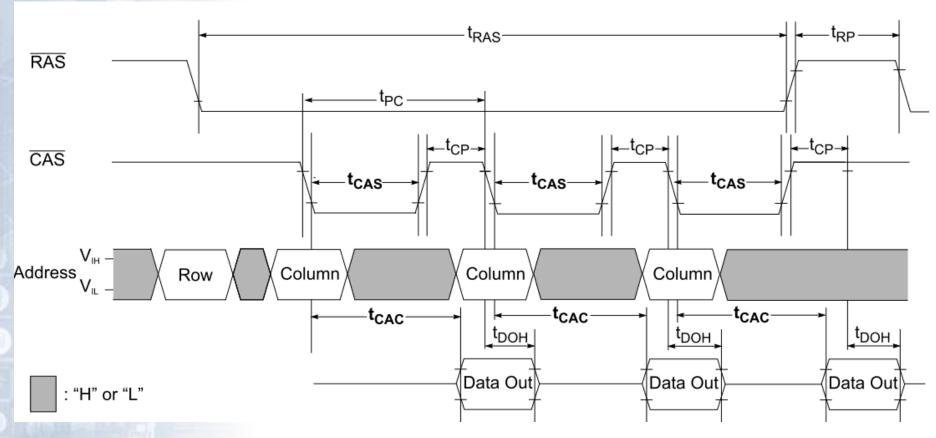

# Tempi di Accesso FPM

- t<sub>RAC</sub> (Random Access): Accesso completo ad un singolo dato da quando si attiva la linea RAS

- t<sub>CAC</sub> (Column Access): Accesso ad un dato da quando si attiva la linea di colonna CAS

- t<sub>PC</sub> (Fast Page Cicle Time):ciclo tra due operazioni consecutive (t<sub>CAS</sub> + t<sub>CP</sub>) (CAS minimo + column precharge) ove : t<sub>CAS</sub> > t<sub>CAC</sub>

t<sub>RP</sub>: Row precharge o recovering time (tempo prima di passare ad un'altra

riga)

# Tempi di Accesso EDO DRAM

- Molto simile FP ma con: t<sub>CAS</sub> < t<sub>CAC</sub>

- t<sub>PC</sub> risulta migliorato

## **Paragone DRAM**

Figure 9: FPM Read Timing

Figure 10: EDO Read Timing

Figure 11: Burst EDO Read Timing

Figure 12: SDR SDRAM Read Operation Clock Diagram (CAS-

## **SDRAM**

512 digit lines

## Memorie NON Volatili

- A Maschera ROM

- PROM a fusibile (Fuse/AntiFuse)

- EPROM con MOS a gate Flottante

- Cancellabili tramite UV

- EEPROM Cancellabili elettricamente

- FLASH: variazioni di EEPROM

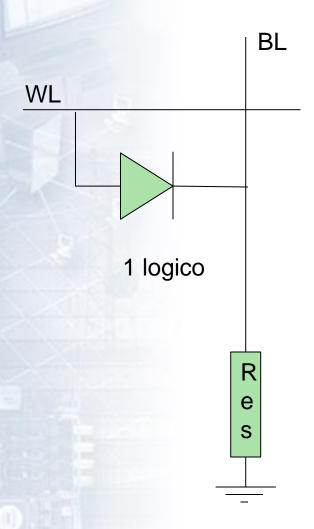

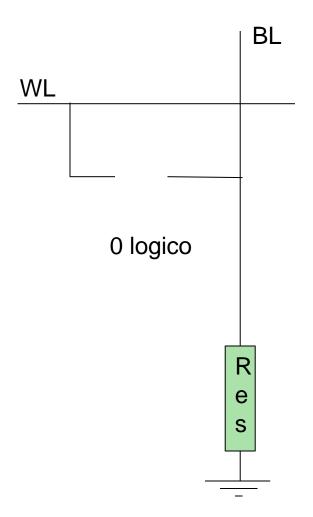

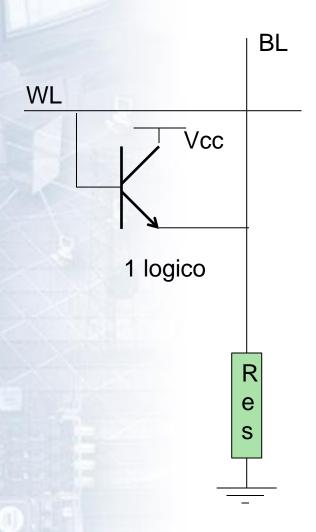

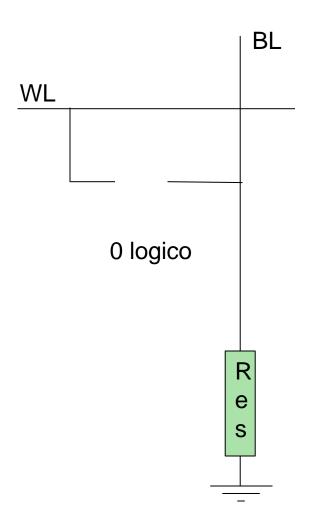

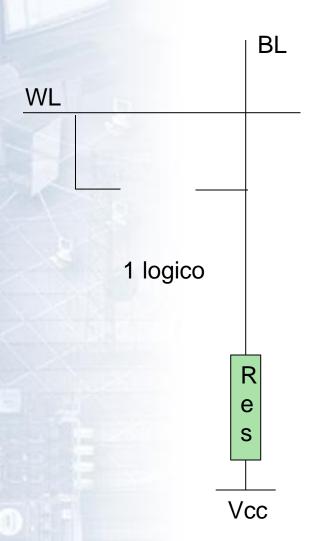

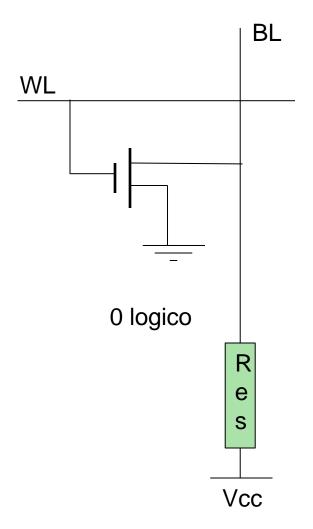

## Cella a Diodo

## Cella a BJT

## Cella a MOS

## Cella PROM

- Programmabile una sola volta

- Si pone in serie all' elemento attivo un fusibile (o un anti-fusibile)

- Gli errori non si correggono

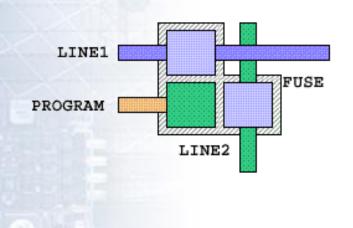

#### **Fuse**

- Le linee del dispositivo sono in origine tutte connesse

- La programmazione consiste nel "BRUCIARE" (fuse) alcune connessioni in modo tale da mantenere solo quelle necessarie

- La programmazione avviene mediante una tensione più elevata di quella di normale funzionamento

LINE1

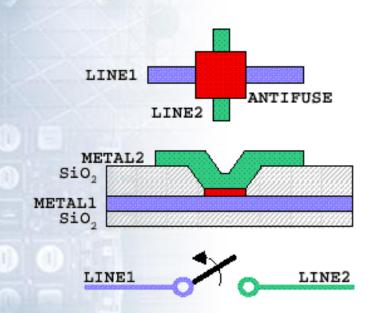

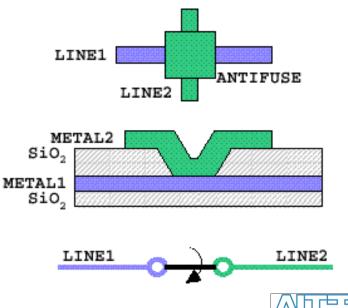

### **Antifuse**

- Le linee del dispositivo sono in origine tutte disconnesse

- La programmazione consiste nel "CREARE" (antifuse) le connessioni necessarie

- La programmazione avviene mediante una tensione più elevata di quella di normale funzionamento

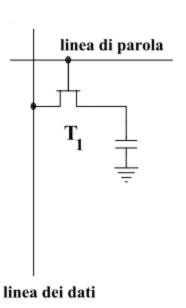

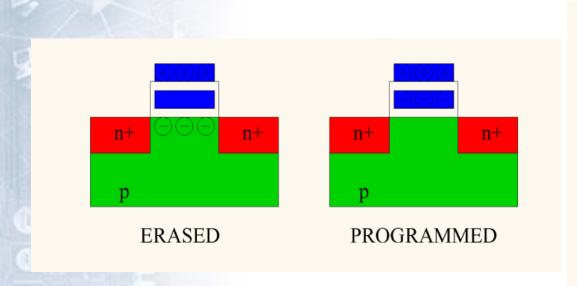

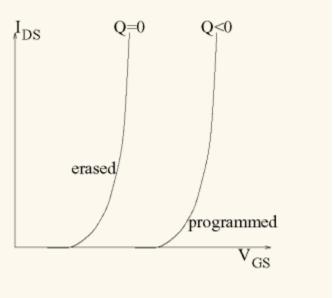

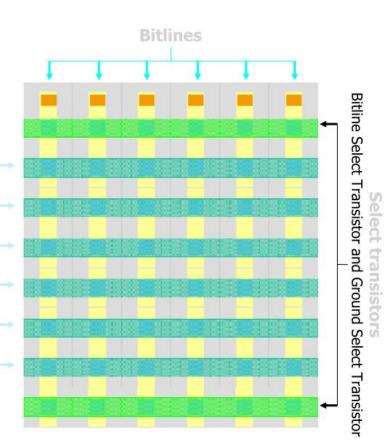

## Cella EPROM

La tensione di soglia dipende dalla carica depositata nel FG

## Iniezione di Carica

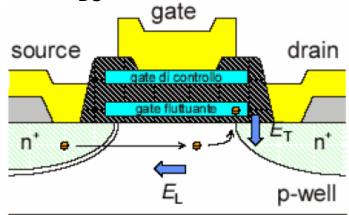

#### Elettroni Caldi (HEI)

- Elevata intensità di campo elettrico tra S e D (100kV/cm)

- La ionizzazione da impatto crea coppie elettrone lacuna ad alta energia

- Le cariche negative (elettroni) indirizzate dalla carica positiva presente su G possono attraversare la barriera di potenziale ed entrare nel FG

- Es.  $V_G = 10V$ ;  $V_S = 0$ ;  $V_D = 5V$ ;  $V_B = 0$ ;

- Pro: veloce, affidabile, poco dipendente dal processo

- Contro: alta corrente I<sub>DS</sub>

## Iniezione di Carica

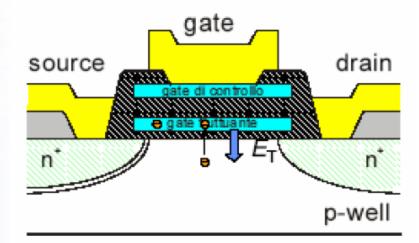

- Effetto Tunnel (Fowler Nordheim)

- Elevata intensità di campo elettrico tra G e D

- Si aumenta la probabilità che qualche elettrone attraversi la barriera di potenziale

- Es.  $V_G=20-30V$ ;  $V_B=0$ ; D e S flottanti

- Pro: correnti basse (può essere impiegato per più celle contemporaneamente)

- Contro: richiede tensioni elevate, minore affidabilità della memoria, più dipendente dai parametri di processo

## Cancellazione

- Il meccanismo HEI non è invertibile

- Cancellazione

- O mediante raggi UV

- La cancellazione può richiedere diversi minuti

- I cicli di programmazione/cancellazione risultano limitati (qualche migliaio)

- O mediante effetto tunnel

- Es:  $V_G = -8V$ ;  $V_S = 5$ ;  $V_B = 5$  D: flottante

## Celle EEPROM

- Sfrutta l'effetto tunnel

- Lo strato di ossido è più sottile in corrispondenza del Drain per agevolare l'effetto tunnel

- Richiede l'uso di un ulteriore Transistor di selezione

- Problemi legati alla cancellazione

- La cella occupa maggior spazio

- Usato anche in fase di lettura

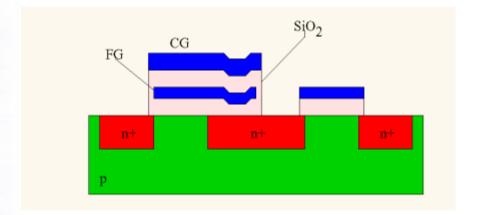

### **Celle Flash**

- Non Usano il Transistor di Controllo (sono più compatte)

- Le celle vengono cancellate a blocchi

- Si dividono in due tipologie

- NOR (Transistor accessibili singolarmente)

- Densità medio bassa

- Veloci

- Utili per memorizzare Codici (es. BIOS)

- NAND (Transistors connessi in serie)

- Densità medio alta

- Facilitato l'accesso seriale alle info

- Accesso Random lento, Accesso per pagina più elevato

- Utili per salvataggio dati

#### Single NOR Flash cell

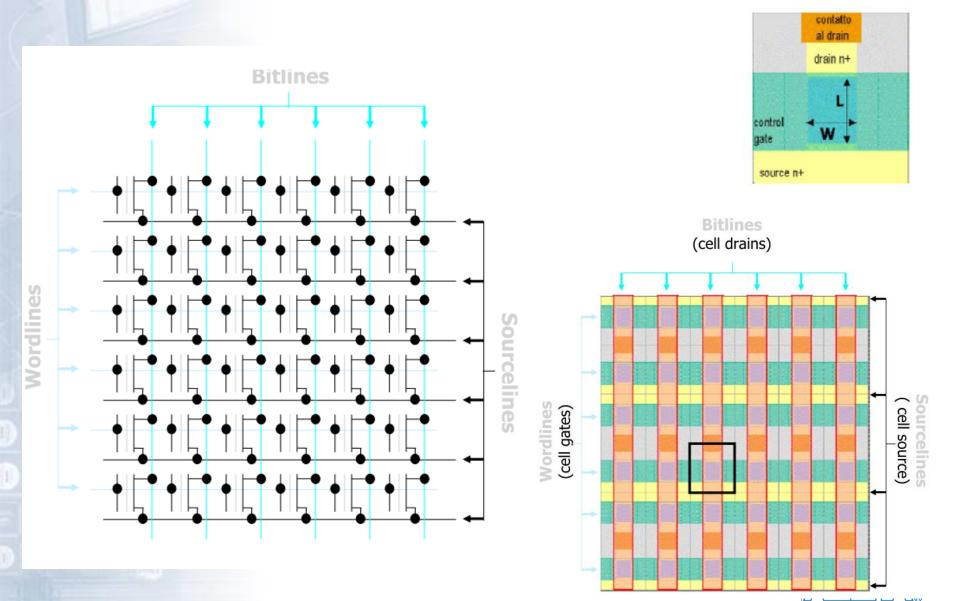

### **NOR Flash structure**

### **NOR Flash**

- Celle indirizzabili singolarmente

- Accessibili

- "word line": Connessione dei GATE posti in riga

- "bit line": Connessione dei Drain posti in colonna

- "source line": Connessione dei Source di un certo settore

- Programmazione mediante moltiplicazione a valanga

- Cancellazione a settori mediante effetto tunnel

- Read:  $V_G=5$ ,  $V_D=1$ ,  $V_S=0$

- si paragona quindi la corrente con una corrente di riferimento

- Program:  $V_G=9$ ,  $V_D=5$ ,  $V_S=0$

- Erase: esistono varie tecniche

- $V_S=12$ ,  $V_G=V_B=0$ ,  $V_D=float$

- $V_S=4$ ,  $V_G=-8$ ,  $V_B=0$ ,  $V_D=float$

- $V_G = -8$ ,  $V_S = V_D = V_B = 8$ ,

- (source erase)

- (negative gate erase)

- (channel erase)

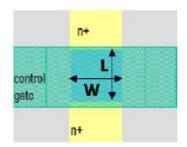

## Single NAND Flash cell

## **NAND Flash structure**

Laddove nella NOR c'era un singolo transistor Ora c'e'

- una serie di transistors

- •1 Bitline select +

- 1 Ground select

Programmazione tramite effetto tunnel

#### Per la lettura:

- Si pongono a tutti i Tr di una serie V<sub>G</sub> superiore alla tensione di soglia superiore

- Si pone al Transistor in analisi V<sub>G</sub> intermedio alle due tensioni di soglia

- Si paragona la corrente con una corrente di riferimento

Facilitato l'accesso a sequenze di dati

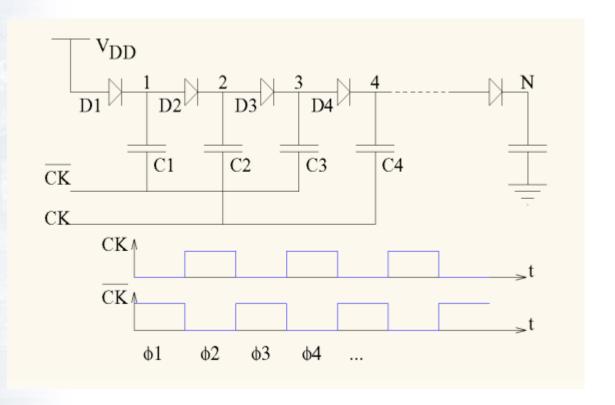

## Circuiti ausiliari

Per ottenere elevate tensioni si usano circuiti a pompa di carica